# UBA2013/L3

# HB driver IC with PFC for fluorescent rings

Rev. 00.01 — 23 February 2007

**Preliminary data sheet**

## 1. General description

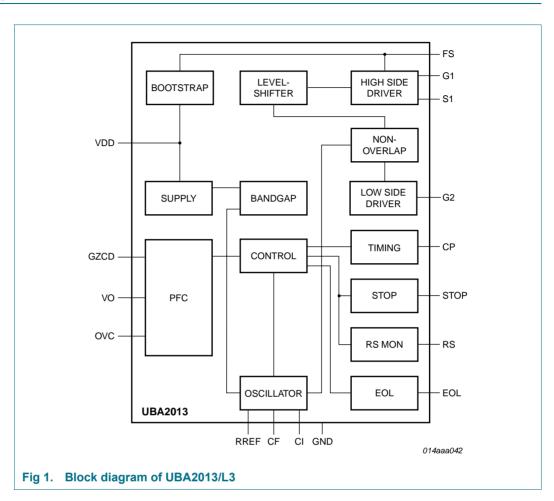

The UBA2013/L3 is a high voltage IC intended to drive and control fluorescent lamps. The IC can handle both cold and warm ignition of the lamp. It contains a  $T_{ON}$ -controlled PFC function, a half bridge controller circuit with level shifter and an internal bootstrap diode to drive an external half bridge. UBA2013/L3 also offers a functionality to properly handle fault conditions such as capacitive mode switching, end-of-lamp-life and overcurrent. UBA2013/L3 is designed for wide-input mains voltage (120 V - 277 V) applications.

## 2. Features

#### 2.1 Half bridge

- Suitable for cold and warm ignition

- Adjustable preheat time

- Adjustable ignition voltage

- Integrated bootstrap function

- Protection for lamp failure and end-of-life

- Adjustable preheat current

- Single ignition attempt

- Automatic restart after relamping

- Protection for capacitive mode

## 2.2 PFC

- Three pin PFC controller using T<sub>ON</sub> control

- Critical mode operation

#### Overvoltage/overcurrent protection

## 3. Applications

The UBA2013/L3 can provide the drive and control function for a wide range of half bridge based ballast applications at different mains voltages.

## 4. Ordering information

| Table 1. Ordening mormation |                    |                                                           |          |  |

|-----------------------------|--------------------|-----------------------------------------------------------|----------|--|

| Type number                 | ype number Package |                                                           |          |  |

|                             | Name               | Description                                               | Version  |  |

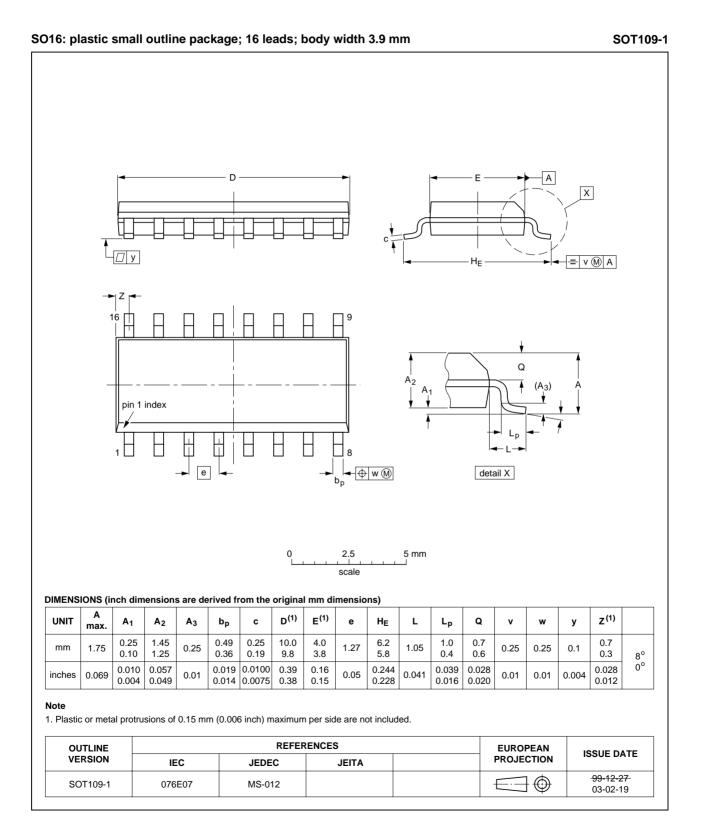

| UBA2013T                    | SO16               | plastic small outline package; 16 leads; body width 3.9mm | SOT109-1 |  |

#### Table 1. Ordering information

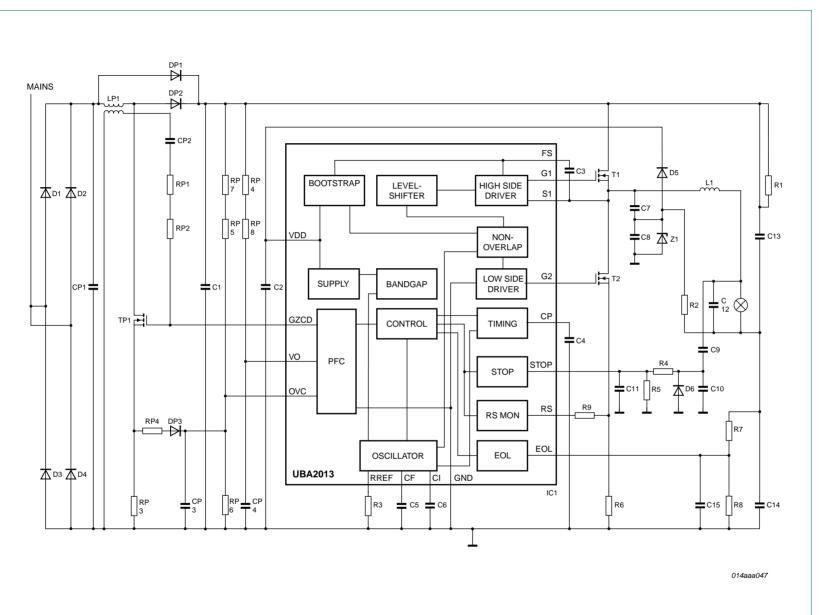

# 5. Block diagram

# 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

#### Table 2. Pin description

|        | i m decemption |                                  |

|--------|----------------|----------------------------------|

| Symbol | Pin            | Description                      |

| VO     | 1              | PFC output voltage sensing       |

| OVC    | 2              | PFC overvoltage/current          |

| CF     | 3              | Oscillator capacitor             |

| CI     | 4              | Integrating capacitor            |

| CP     | 5              | Timing capacitor                 |

| EOL    | 6              | End-of-life                      |

| RREF   | 7              | Reference resistor               |

| STOP   | 8              | Stop                             |

| S1     | 9              | Source high side transistor (T1) |

| FS     | 10             | High side floating supply        |

| G1     | 11             | Gate high side transistor (T1)   |

| RS     | 12             | Current sensor                   |

| G2     | 13             | Gate low side transistor (T2)    |

| VDD    | 14             | Low voltage supply               |

| GND    | 15             | Ground                           |

| GZCD   | 16             | PFC gate and ZCD                 |

|        |                |                                  |

## 7. Functional description

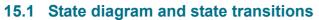

#### 7.1 Start-up state

Initial start up can be achieved by means of charging the VDD low voltage supply capacitor (C2 in the application diagram Figure 6) via an external start-up resistor. Start-up state is one of the non-oscillating sub-states. MOSFET T2 conducts and T1 is non-conducting, ensuring bootstrap capacitor C3 to be charged. In this state the circuit will be reset. The GZCD pin is pulled down and  $I_{VO(ref)}$  is not active. If  $V_{STOP} < V_{STOP(reset)}$  at the transition of  $V_{DD}$  exceeding  $V_{DD(start)}$ , the IC will enter the oscillating state. If not it will enter the stop state.

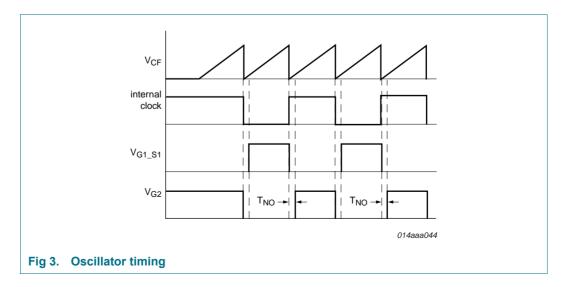

#### 7.2 Half bridge oscillator

Oscillation of the half bridge is controlled by a built-in current-controlled oscillator which generates a sawtooth waveform at the CF pin. The sawtooth frequency is twice the half bridge frequency, and is determined by the capacitor at the CF pin and the current-out of pin CF, as controlled by the voltage at the CI pin. Frequency modulation is achieved by charging and discharging the CI capacitor. The IC brings MOSFETs T1 and T2 alternately into conduction with a duty factor of just below 50% each (except for situations where  $V_{RS}$  exceeds  $V_{RS(clamp)}$ ). Figure 3 represents the timing of the IC. The circuit block 'non-overlap' generates a non-overlap time  $t_{no}$  that ensures periods of exclusive conduction of T1 or T2. Time  $t_{no}$  depends on the reference current  $I_{RREF}$ .

### 7.3 Oscillating state

Oscillating state can be entered:

- when in the startup state V<sub>STOP</sub> < V<sub>STOP</sub>(reset) at the moment V<sub>DD</sub> reaches V<sub>DD(start)</sub>

- when in the VddLow state, when  $V_{STOP} < V_{STOP(ref)}$  at the moment  $V_{DD}$  reaches  $V_{DD(start)}$ .

The oscillating state has three sub-states: the preheat state, the ignition state and the burn state. The circuit always starts oscillating in the preheat state.

#### 7.4 Preheat state

The circuit starts oscillating at the half-bridge frequency  $f_{start}$  (approximately 2.5 x  $f_B$ ). The frequency gradually decreases until a user-defined value of the preheat current is reached. The slope of the decrease in frequency is determined by the capacitor at the CI pin. During preheat, the circuit monitors the inductor current by measuring the voltage across external resistor RS at the end of the conduction of T2 with decision level  $V_{RS(ph)}$ . The frequency is decreased for as long as  $V_{RS} < V_{RS(ph)}$ . The frequency is increased for  $V_{RS} > V_{RS(ph)}$ . During preheat the STOP pin is discharged to ground via a switch with an on resistance of  $R_{STOP(disch)}$ . The cycle-by-cycle excess charge control mechanism described in the ignition state is not active during the preheat state. The preheat time is determined by capacitor CP. For cold ignition the preheat time can be reduced by choosing a smaller CP capacitor. The circuit can be locked in the preheat state by connecting pin CP to ground.

#### 7.5 Ignition state

After the preheat time the ignition state is entered and the frequency will sweep down due to charging of the capacitor at the CI pin with the internally fixed current  $I_{Cl(charge)}$ . During this decrease in frequency, the circuit approaches the resonance frequency of the load. This will cause a high voltage across the load, which normally ignites the lamp.

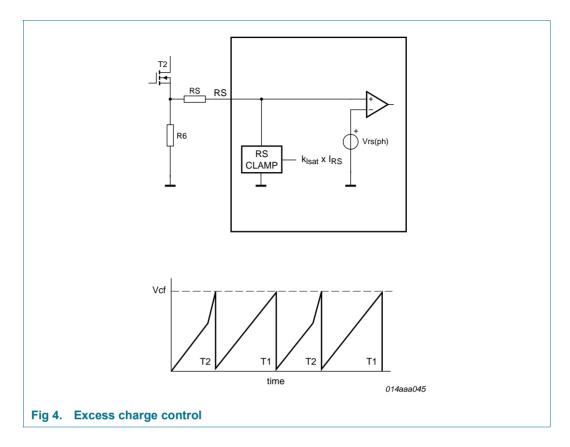

In order to limit voltages and currents in the resonant circuit in case of non- or delayed ignition, a cycle-by-cycle excess charge control mechanism is used to prevent deep saturation and to limit the lamp voltage. When the voltage at pin RS exceeds  $V_{RS(clamp)}$  the impedance of the pin changes from essentially infinite to essentially zero. If a current is flowing into pin RS during the on-state of T2, a fraction  $k_{lsat}$  of that current will be fed into the capacitor  $C_{CF}$  at pin CF in addition to the oscillator current already flowing into  $C_{CF}$ . The amount of current fed into  $C_{CF}$  depends on the voltage across RS and the value of resistor R, see Figure 4. The increased current rapidly (but not instantly) ends the oscillator half-cycle, after which T2 is switched off. The on-time of T1 is not affected and thus the half bridge will run asymmetrically, see Figure 4.

#### 7.6 Burn state

At the end of the ignition time, the burn state is entered. In this state the voltage at the CI pin will continue to increase until a clamp level is reached corresponding to the minimum frequency  $f_B$ . The circuit will continue to oscillate at the minimum frequency, unless capacitive mode is detected. In the burn state the CP pin is pulled to ground with a discharge impedance  $R_{CP(disch)}$ . The EOL protection is enabled. The excess charge control mechanism will remain active.

#### 7.7 Capacitive mode protection

Capacitive mode protection is active in all oscillating states. The signal across resistor RS (R6 in the application diagram of Figure 6) also gives information about the switching behavior of the half bridge. If the voltage across resistor RS is not below  $V_{RS(cap)}$  at the moment of turn-on of T2, the capacitive mode detection circuit assumes the circuit to be in capacitive mode. Upon capacitive mode detection CI is gradually discharged and instantly the frequency gradually increases as long as capacitive mode is detected. The frequency decreases gradually down to the minimum frequency if no capacitive mode is detected. Detecting capacitive mode at the maximum frequency will activate the internal current  $I_{STOP(ch)}$  that charges the STOP pin.

#### 7.8 Stop function

For all oscillating states the IC will enter the stop state for  $V_{STOP} > V_{STOP(ref)}$ . Note that there is no internal stop timing. An external stop timing can be obtained via the RC time of the network R4, R5 and C11, see the application diagram in Figure 6. During preheat the

STOP pin is discharged to ground via a switch with on-resistance  $R_{STOP(disch)}$ . In case of a VO-low condition (see <u>Section 7.15</u>), the STOP pin is discharged with a current  $I_{STOP(dis)}$ . Apart from the preheat state or a VO-low condition, the IC will not discharge the STOP pin at any VDD.

#### 7.9 End-of-life protection

The end-of-life circuit is only active in the burn state and consists of a voltage window comparator circuit. It compares the voltage at the EOL pin with two internal reference voltages. When the voltage at the EOL pin is above  $V_{EOL(high)}$  or below  $V_{EOL(low)}$  the 'end-of-life' protection circuit activates the internal current source  $I_{STOP(ch)}$  that charges the STOP pin. The 'end-of-life' protection is not active in case of a VO-low condition (see Section 7.15).

#### 7.10 Non-oscillating state

Transitions to the non-oscillating state are always made during a G2 high condition in the half bridge (lower MOSFET T2 conducting). In the non-oscillating state T1 is off, T2 is on, the PFC control function is stopped by pulling the GZCD pin down to ground continuously, and reference current  $I_{VO(ref)}$  is switched off. Additionally, the CP and CI pins are discharged to ground. The non-oscillating state has three sub-states: the start-up state, the stop state and the VddLow state.

#### 7.11 Start-up state

Described at the beginning of this functional description.

#### 7.12 Stop state

The circuit will enter the stop state:

- when in any of the oscillating states V<sub>STOP</sub> > V<sub>STOP(ref)</sub>

- when in the VddLow state V<sub>STOP</sub> > V<sub>STOP(ref)</sub> at the moment V<sub>DD</sub> exceeds V<sub>DD(start)</sub>

- when in the startup state V<sub>STOP</sub> > V<sub>STOP(reset)</sub> at the moment V<sub>DD</sub> exceeds V<sub>DD(start)</sub>.

In the stop state, a clamp circuit is active, limiting the voltage at the VDD pin to  $V_{DD(clamp)}$ . The IC goes from the stop state into the startup state if  $V_{DD}$  drops below  $V_{DD(reset)}$ .

#### 7.13 VddLow state

The circuit will enter VddLow state in any of the oscillating states when  $V_{DD}$  drops below  $V_{DD(low)}$ . The circuit then goes from VddLow state to:

- the startup state if V<sub>DD</sub> drops below V<sub>DD(reset)</sub>

- the stop state if V<sub>STOP</sub> > V<sub>STOP(ref)</sub> at the moment V<sub>DD</sub> exceeds V<sub>DD(start)</sub>, or

- the preheat state if V<sub>STOP</sub> < V<sub>STOP(ref)</sub> at the moment V<sub>DD</sub> exceeds V<sub>DD(start)</sub>.

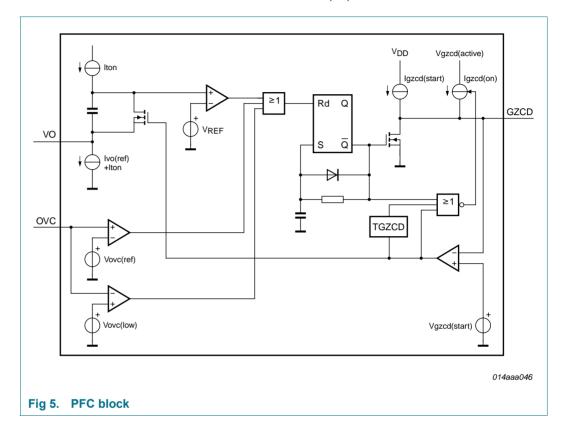

#### 7.14 PFC function

The internal PFC control block provides a  $T_{ON}$  controlled, critical mode power factor correction controller. The  $T_{ON}$  is set by the voltage at the VO pin. The duration of the  $T_{ON}$  pulse decreases linearly with increasing  $V_{VO}$ . The  $V_{VO}$  voltage is the result of an error current through the compensation impedance connected at the VO pin. This error current is the difference between a current proportional to the output voltage of the PFC pulling the VO pin high and an internal reference current  $I_{VO(ref)}$  pulling the VO pin low.

The external MOSFET is primarily driven via the secondary winding on the inductor L<sub>P1</sub>. The T<sub>ON</sub> timing starts the moment V<sub>GZCD</sub> exceeds V<sub>GZCD(start)</sub> (below the threshold of the external MOSFET). The external MOSFET is turned on and current builds up in the inductor L<sub>P1</sub>. At the end of T<sub>ON</sub> the output driver pulls the GZCD pin down during a defined time T<sub>OFF</sub>. This turns off the external MOSFET. The inductor current I<sub>LP1</sub> now flows through the boost diode DP2. The polarity of the voltage across the secondary winding changes to negative, keeping the external MOSFET in the off state. As long as V<sub>GZCD</sub> is below V<sub>GZCD(start)</sub> the T<sub>ON</sub> timing is reset. The current in the inductor decreases linearly to below zero. Just after the zero crossing the polarity of the voltage across the secondary winding turning on the external MOSFET and completing the cycle.

$T_{ON}$  varies linearly from  $T_{ON(max)}$  to  $T_{ON(min)}$  in the range of  $V_{VO}$  from  $V_{VO(low)}$  to  $V_{VO(low)} + \Delta V_{VO}$ . Above a voltage  $V_{VO(off)}$  (> $V_{VO(low)} + \Delta V_{VO}$ ) at the VO pin,  $T_{ON}$  is zero and the GZCD pin is continuously pulled down.

The OVC pin is intended for over-voltage and/or over-current protection. The voltage at the OVC pin is compared to a reference voltage  $V_{OVC(ref)}$ . For  $V_{OVC} > V_{OVC(ref)}$  the GZCD pin is pulled down within a time  $T_{OVC}$ . As long as  $V_{OVC} > V_{OVC(ref)}$  the GZCD pin will be continuously pulled down by the output driver. Additionally, the OVC pin provides protection against an accidental open circuit of the external OVC divider of the PFC output voltage. As long as  $V_{OVC} < V_{OVC(low)}$  the GZCD pin is continuously pulled down by the output driver.

In order to prevent persistent ambiguous drive signals for the external MOSFET, for V<sub>GZCD</sub> > V<sub>GZCD(start)</sub> the GZCD pin is charged after a delay of T<sub>GZCD</sub> with a current of I<sub>GZCD(on)</sub> up to a voltage of V<sub>GZCD(active)</sub> (above the threshold of the external MOSFET). Note that the voltage at the GZCD pin is not clamped at V<sub>GZCD(active)</sub>: the secondary winding on the inductor L<sub>P1</sub> can take the GZCD pin up to V<sub>DD</sub>.

The PFC function is self-starting by means of a current source  $I_{GZCD(start)}$  (<<  $I_{GZCD(on)}$ ) which, under oscillation conditions, continuously charges the GZCD pin. In any of the non-oscillating states the current sources  $I_{GZCD(start)}$  and  $I_{VO(ref)}$  are off and the GZCD pin is continuously pulled down. In oscillating conditions the positive voltage at the VO pin is clamped at a level  $V_{VO(clamp)}$ : in non-oscillating conditions, the positive voltage at the VO pin is clamped at a level <  $V_{VO(off)}$ .

#### 7.15 VO-low condition

In order to prevent unintended stopping in case of the mains voltage being too low for the PFC stage to maintain its intended output voltage, this condition is detected in the oscillating state by the current sunk into the VO pin dropping below  $k_{VO}$ \*I<sub>VO(ref)</sub>, where the constant  $k_{VO}$  represents a fraction (typ. 95%) of I<sub>VO(ref)</sub>. In case of a VO-low condition:

the end-of-life protection is deactivated,

- the stop level is effectively raised by discharging the STOP pin with a current  $I_{\mbox{STOP}(\mbox{dis})}.$

The VO-low condition is overruled when V<sub>OVC</sub><V<sub>OVC(low)</sub>.

#### 7.16 State and transition diagrams

See Section 16.1.

#### 7.17 Charge coupling

Via parasitic capacitive coupling to high-voltage AC signals present in the application, a repetitive AC charge injection might occur at the IC-pins. In the typical application of Figure 6, the pins R<sub>REF</sub> and C<sub>F</sub> are most sensitive to this charge injection. For a charge coupling of Q<sub>coupl</sub>, safe functional operation of the IC is guaranteed, irrespective of the current level. Charge coupling at current levels below 50  $\mu$ A will not interfere with the accuracy of the V<sub>RS(cap)</sub> and V<sub>RS(ph)</sub> levels. Charge coupling at current levels below 20  $\mu$ A will not interfere with the accuracy of any parameter.

## 8. Limiting values

| Symbol                | Parameter                                                                                                       | Conditions                                      |            | Min                 | Max                  | Unit        |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|---------------------|----------------------|-------------|

| V <sub>FS</sub>       | High-side floating supply voltage                                                                               | Operating<br>t<0.5s                             |            | 0                   | 570<br>630           | V           |

| V <sub>RS</sub>       | Voltage at pin RS                                                                                               |                                                 | [3]        | 0                   | $V_{BE}$             | V           |

| I <sub>RS</sub>       | Current in pin RS                                                                                               | t<1.0μs                                         | [4]        | -10                 | 10                   | mA          |

| V <sub>G1</sub>       | Voltage at pin G1                                                                                               |                                                 | [3]        | $V_{S1}$ - $V_{BE}$ | V <sub>FS</sub>      | V           |

| V <sub>G2</sub>       | Voltage at pin G2                                                                                               |                                                 | [3]        | -V <sub>BE</sub>    | V <sub>VDD</sub>     | V           |

| V <sub>VDD</sub>      | Low-voltage supply                                                                                              | t<0.5s over<br>lifetime                         |            | 0                   | 15                   | V           |

| V <sub>VDD</sub>      | Low-voltage supply                                                                                              | In stop state                                   |            | 0                   | 14                   | V           |

| I <sub>VDD</sub>      | Clamp current in pin VDD                                                                                        |                                                 |            |                     | 5                    | mA          |

| V <sub>GZCD</sub>     | Voltage at pin GZCD                                                                                             |                                                 | [3]        | -V <sub>BE</sub>    | $V_{VDD}$            | V           |

| V <sub>OVC</sub>      | Voltage at pin OVC                                                                                              |                                                 |            | 0                   | 5                    | V           |

| I <sub>VO</sub>       | Current in pin VO                                                                                               | V <sub>VDD</sub> = 0V to<br>V <sub>VDDmax</sub> |            | 0                   | 200                  | μA          |

| I <sub>CF</sub>       | Current in pin CF                                                                                               | V <sub>VDD</sub> = 0V to<br>V <sub>VDDmax</sub> |            | 0                   | 200                  | μA          |

| I <sub>EOL</sub>      | Current in pin EOL                                                                                              | V <sub>VDD</sub> = 0V to<br>V <sub>VDDmax</sub> |            | -1                  | 1                    | mA          |

| SR                    | Slew rate at pins S1, G1 and FS                                                                                 | With respect to<br>ground                       |            | -4                  | 4                    | V/ns        |

| Tj                    | Junction temperature                                                                                            |                                                 |            | -25                 | 150                  | °C          |

| T <sub>amb</sub>      | Ambient temperature                                                                                             |                                                 |            | -25                 | 100                  | °C          |

| T <sub>stg</sub>      | Storage temperature                                                                                             |                                                 |            | -55                 | 150                  | °C          |

| V <sub>esd(HBM)</sub> | HBM electrostatic handling<br>voltage<br>pin EOL and G1<br>pins FS, S1, VDD and G2<br>pins VO, OVC, CF, CI, CP, |                                                 | <u>[1]</u> |                     | <500<br>1000<br>2000 | V<br>V<br>V |

| V <sub>esd(MM)</sub>  | RREF, STOP, RS, GZCD<br>MM electrostatic handling<br>voltage                                                    |                                                 | [2]        |                     |                      |             |

|                       | pin EOL                                                                                                         |                                                 |            |                     | 50                   | V           |

|                       | pins FS, G1, S1, VDD and<br>G2<br>pins VO, OVC, CF, CI, CP,                                                     |                                                 |            |                     | 100                  | V           |

|                       | RREF, STOP, RS, GZCD                                                                                            |                                                 |            |                     | 200                  | V           |

| Q <sub>coupl</sub>    | Charge coupling at pins<br>RREF and CF                                                                          | Operating                                       |            | -8                  | 8                    | рС          |

| R <sub>RREF</sub>     | Reference resistor                                                                                              |                                                 |            | 22                  | 47                   | kΩ          |

[1] In accordance with the Human Body Model (HBM): i.e. equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

[2] In accordance with the Machine Model (MM): i.e. equivalent to discharging a 200 pF capacitor through a 10  $\Omega$  series resistor and a 0.75  $\mu$ H inductor.

- [3] At  $T_{amb}$  = 25 °C the typical V<sub>BE</sub> is 0.7 V.

- [4] At negative RS currents (typ. < -5 mA) capacitive-mode protection can be triggered.

## 9. Thermal characteristics

| Table 4.             | Thermal characteristics                          |             |     |      |

|----------------------|--------------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                        | Conditions  | Тур | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient SO16 | in free air | 100 | K/W  |

| $R_{th(j-pin)}$      | thermal resistance from junction to pin SO16     | in free air | 50  | K/W  |

## **10. Characteristics**

#### Table 5.Characteristics

$T_{amb}$  = 25 °C;  $V_{VDD}$  = 13.0 V;  $C_{CF}$  = 100 pF;  $R_{RREF}$  = 33 k $\Omega$ ;  $C_{CP}$  = 100 nF;  $C_{Cl}$  = 100 nF; all voltages referenced to ground unless otherwise specified.

|                            | -                                  |                                            |               |      |       |      |      |

|----------------------------|------------------------------------|--------------------------------------------|---------------|------|-------|------|------|

| Symbol                     | Parameter                          | Conditions                                 |               | Min  | Тур   | Мах  | Unit |

| High-voltage               | supply                             |                                            |               |      |       |      |      |

| I <sub>L1</sub>            | Leakage current: high-voltage pins | FS, G1, S1 = 630 V, V <sub>VDD</sub> = 0 V |               |      |       | 15   | μA   |

| Start-up state             |                                    |                                            |               |      |       |      |      |

| V <sub>DD(start)</sub>     | Start of oscillation               |                                            |               | 12.1 | 12.6  | 13.1 | V    |

| V <sub>DD(low)</sub>       | Stop of oscillation                |                                            |               | 9.7  | 10.2  | 10.7 | V    |

| V <sub>DD(hys)</sub>       | Start-stop hysteresis              |                                            |               | 2.2  | 2.4   | 2.6  | V    |

| I <sub>VDD(nonosc)</sub>   | Non-oscillating current            | VVDD = 12 V                                | [2]           | 100  | 150   | 200  | μA   |

| V <sub>DD(clamp)</sub>     | Clamp voltage VDD                  | At 5 mA non-oscillating                    |               | 10.0 | 12.0  | 14.0 | V    |

| V <sub>DD(reset)</sub>     | Reset voltage                      |                                            | [10]          | 4.5  | 5.5   | 6.5  | V    |

| Preheat volta              | ge                                 |                                            |               |      |       |      |      |

| f <sub>start</sub>         | Starting frequency                 | V <sub>CI</sub> = 0                        | <u>[1]</u>    | 101  | 112.5 | 124  | kHz  |

| T <sub>PH</sub>            | Preheat time                       | C <sub>CP</sub> = 100 nF                   |               | 574  | 674   | 796  | ms   |

| I <sub>CP(charge)</sub>    | Charge current at CP pin           | V <sub>CP</sub> = 1.0 V                    |               |      | 6.0   |      | μA   |

| I <sub>CP(discharge)</sub> | Discharge current at CP pin        | V <sub>CP</sub> = 3.5 V                    |               |      | 6.0   |      | μA   |

| $\Delta V_{CP(pk)}$        | Peak voltage difference at CP pin  | When timing                                |               |      | 2.45  |      | V    |

| V <sub>CP(min)</sub>       | CP comparator level low            |                                            |               | 1.10 | 1.25  |      | V    |

| V <sub>RS(ph)</sub>        | Control voltage at RS pin          |                                            | <u>[5]</u>    | 365  | 400   | 435  | mV   |

| Ignition state             |                                    |                                            |               |      |       |      |      |

| T <sub>IG</sub>            | Ignition time                      | C <sub>CP</sub> = 100 nF                   |               | 512  | 611   | 730  | ms   |

| V <sub>RS(clamp)</sub>     | Saturation current detection level | At I <sub>RS(ig)</sub> = 0.5 mA            |               |      | 0.75  |      | V    |

| k <sub>lsat</sub>          | Saturation control current gain    |                                            | <u>[6]</u>    | 0.45 | 0.50  | 0.55 | A/A  |

| Burn state                 |                                    |                                            |               |      |       |      |      |

| f <sub>B</sub>             | Bottom frequency                   |                                            | <u>[1]</u>    | 43.6 | 45.0  | 46.4 | kHz  |

| T <sub>NO</sub>            | Non-overlap time                   |                                            |               | 1.05 | 1.40  | 1.75 | μS   |

| SYM f <sub>B</sub>         | Symmetry half bridge               |                                            | <u>[1][9]</u> | 0.9  | 1.0   | 1.1  |      |

| SYM T <sub>NO</sub>        | Symmetry non-overlap time          |                                            | [11]          |      | 1.0   |      |      |

|                            |                                    |                                            |               |      |       |      |      |

#### Table 5. Characteristics ...continued

$T_{amb}$  = 25 °C;  $V_{VDD}$  = 13.0 V;  $C_{CF}$  = 100 pF;  $R_{RREF}$  = 33 k $\Omega$ ;  $C_{CP}$  = 100 nF;  $C_{CI}$  = 100 nF; all voltages referenced to ground unless otherwise specified.

| Symbol                          | Parameter                         | Conditions                 |                | Min   | Тур   | Мах   | Unit |

|---------------------------------|-----------------------------------|----------------------------|----------------|-------|-------|-------|------|

| I <sub>tot</sub>                | Total supply current              |                            | <u>[1][7]</u>  |       | 1.5   | 2.0   | mA   |

| I <sub>CI(charge)</sub>         | Charge current at CI pin          | V <sub>CI</sub> = 1.5 V    |                | 36    | 44    | 52    | μA   |

| I <sub>CI(discharge)</sub>      | Discharge current at CI pin       | V <sub>CI</sub> = 1.5 V    |                | 74    | 90    | 106   | μA   |

| $\Delta I_{CF} / \Delta V_{CI}$ | CI transconductance               | V <sub>CI</sub> = 1.5 V    |                |       | 12    |       | μA/V |

| V <sub>RS(cap)</sub>            | Capacitive-mode control voltage   |                            | [8]            | -40   | -20   | 0     | mV   |

| V <sub>RREF</sub>               | Reference voltage                 |                            |                | 2.425 | 2.500 | 2.575 | V    |

| V <sub>G1(on)</sub>             | On voltage at pin G1              | I <sub>G1</sub>   = 1 mA   |                | 10.5  |       |       | V    |

| V <sub>G1(off)</sub>            | Off voltage at pin G1             | I <sub>G1</sub>   = 1 mA   |                |       |       | 0.3   | V    |

| VG2(on)                         | On voltage at pin G2              | I <sub>G2</sub>   = 1 mA   |                | 10.5  |       |       | V    |

| VG2(off)                        | Off voltage at pin G2             | I <sub>G2</sub>   = 1 mA   |                |       |       | 0.3   | V    |

| R <sub>G1(on)</sub>             | High side driver on resistance    | V <sub>(G1-S1)</sub> = 3 V |                |       | 250   |       | Ω    |

| R <sub>G1(off)</sub>            | High side driver off resistance   | V <sub>(G1-S1)</sub> = 3 V |                |       | 35    |       | Ω    |

| R <sub>G2(on)</sub>             | Low side driver on resistance     | V <sub>G2</sub> = 3 V      |                |       | 250   |       | Ω    |

| R <sub>G2(off)</sub>            | Low side driver off resistance    | V <sub>G2</sub> = 3 V      |                |       | 35    |       | Ω    |

| V <sub>drop</sub>               | Voltage drop at bootstrap switch  | I <sub>FS</sub> = 5 mA     |                |       | 2.0   |       | V    |

| R <sub>CP(disch)</sub>          | On resistance switch at CP pin    | V <sub>CP</sub> = 0.6 V    |                |       | 120   |       | Ω    |

| Stop and end                    | l-of-life                         |                            |                |       |       |       |      |

| V <sub>STOP(ref)</sub>          | Stop reference level              |                            |                | 1.21  | 1.26  | 1.31  | V    |

| V <sub>STOP(reset)</sub>        | Stop reset level                  |                            | [10]           | 0.95  | 1.00  | 1.05  | V    |

| V <sub>STOP(hys)</sub>          | Stop hysteresis                   |                            | [10]           | 0.20  | 0.25  | 0.30  | V    |

| I <sub>STOP(ch)</sub>           | Stop-charge current source        | V <sub>STOP</sub> = 0.75 V |                | 2.0   | 2.5   | 3.0   | μA   |

| I <sub>STOP(dis)</sub>          | Stop discharge current            | V <sub>STOP</sub> = 0.75 V |                | 0.35  | 0.50  | 0.65  | μA   |

| $R_{\text{STOP}(\text{disch})}$ | On resistance discharge switch    | V <sub>STOP</sub> = 0.5 V  |                | 1.0   | 2.5   | 4.0   | kΩ   |

| $V_{EOL(high)}$                 | High level end-of-life comparator |                            |                | 2.9   | 3.0   | 3.1   | V    |

| V <sub>EOL(low)</sub>           | Low level end-of-life comparator  |                            |                | 1.9   | 2.0   | 2.1   | V    |

| Power-factor                    | control                           |                            |                |       |       |       |      |

| I <sub>VO(ref)</sub>            | Output voltage reference current  | V <sub>VO</sub> = 3.0 V    |                | 97    | 102   | 107   | μA   |

| V <sub>OVC(ref)</sub>           | OVC reference level               |                            |                | 1.21  | 1.26  | 1.31  | V    |

| T <sub>OVC</sub>                | Delay OVC comparator              |                            |                |       | 60    |       | ns   |

| V <sub>VO(low)</sub>            | VO offset voltage                 |                            |                |       | 1.0   |       | V    |

| $\Delta V_{VO}$                 | VO dynamic range                  |                            |                |       | 2.7   |       | V    |

| I <sub>GZCD(start)</sub>        | Start-up current at GZCD pin      | V <sub>GZCD</sub> = 0 V    |                | 35    | 42.5  | 50    | μA   |

| I <sub>GZCD(on)</sub>           | Turn on current at GZCD pin       | V <sub>GZCD</sub> = 3 V    |                |       | 12    |       | μA   |

| V <sub>GZCD(start)</sub>        | GZCD start level                  |                            |                | 1.9   | 2.0   | 2.1   | V    |

| V <sub>GZCD(active)</sub>       | GZCD active level                 | I <sub>GZCD</sub> = 0.5 mA |                |       | 6.4   |       | V    |

| T <sub>GZCD</sub>               | GZCD turn on delay                |                            |                |       | 0.5   |       | μS   |

| T <sub>ON(max)</sub>            | Maximum on time                   | $V_{VO} = V_{VO(low)}$     | [4]            | 20    |       |       | μS   |

| T <sub>ON(min)</sub>            | Minimum on time                   | $V_{VO} = V_{VO(off)}$     | <u>[3][10]</u> |       | 0.4   | 0.5   | μS   |

| I <sub>GZCD(sink)</sub>         | Gate drive sink current           | $V_{GZCD} = 4 V$           |                | 200   |       |       | mA   |

|                                 |                                   |                            |                |       |       |       |      |

#### Table 5. Characteristics ...continued

$T_{amb}$  = 25 °C;  $V_{VDD}$  = 13.0 V;  $C_{CF}$  = 100 pF;  $R_{RREF}$  = 33 k $\Omega$ ;  $C_{CP}$  = 100 nF;  $C_{CI}$  = 100 nF; all voltages referenced to ground unless otherwise specified.

| Symbol                 | Parameter                | Conditions                              | Min  | Тур  | Max  | Unit |

|------------------------|--------------------------|-----------------------------------------|------|------|------|------|

| T <sub>OFF</sub>       | Duration off pulse       |                                         |      | 0.9  |      | μS   |

| V <sub>OVC(low)</sub>  | OVC low voltage          |                                         |      | 120  |      | mV   |

| k <sub>VO</sub>        | VO low factor            |                                         | 0.86 | 0.95 | 0.99 |      |

| V <sub>VO(off)</sub>   | Off voltage PFC          |                                         |      | 3.7  |      | V    |

| V <sub>VO(clamp)</sub> | Active VO clamp voltage  | I <sub>VO</sub> = 200 μA                |      | 4.7  |      | V    |

| V <sub>VO(pas)</sub>   | Passive VO clamp voltage | $I_{VO}$ = 200 $\mu$ A, $V_{VDD}$ = 0 V |      | 3.9  |      | V    |

[1] Excluding situations where the excess charge control mechanism is active.

[2] The non-oscillation current is specified in a temperature range of 0 to 100 °C. For Tj < 0 °C and Tj > 100 °C the maximum start-up current is 350 μA.

[3] Minimum on-time is defined without the external MOSFET.  $V_{GZCD}$  is increased from 0 to 10 V in 1µs.  $T_{ONmin}$  is defined as the time elapsed between  $V_{GZCD}$  exceeding  $V_{GZCD}$ (start) and  $V_{GZCD}$  being pulled below 3 V at turn-off.

- [4] Maximum on-time is defined without the external MOSFET. Parameter is measured with  $V_{VO} = V_{VO(low)}$  and  $V_{GZCD}$  is increased from 0 to 10 V in 1µs.  $T_{ONmax}$  is defined as the time elapsed between  $V_{GZCD}$  exceeding  $V_{GZCD}(start)$  and  $V_{GZCD}$  pulled below 3 V at turn- off.

- [5] Data sampling of  $V_{RS(ph)}$  is performed at the end of conduction of T2 .

- [6] Gain is defined as  $I_{CF}/I_{RS}$  with  $V_{RS}>V_{RS(clamp)}$ .

- [7] Total supply current is specified in a T<sub>i</sub> temperature range of -20 °C to 125 °C at f<sub>B</sub>, excluding gate drive charge.

- [8] Data sampling of  $V_{RS(cap)}$  is performed at the start of conduction of T2 .

- [9] The symmetry SYM  $f_B$  is calculated from the quotient SYM  $f_B = T1_{tot}/T2_{tot}$ , with T1<sub>tot</sub> being the time between turn-off of G2 and the turn-off of G1, and T2<sub>tot</sub> the time between turn-off of G1 and the turn-off of G2.

- [10] Not measured, guaranteed by design.

- [11] The symmetry SYM  $T_{NO}$  is defined as the ratio between deadtime1 and deadtime2. Deadtime1 is the time between turning off G1 and turning on G2. Deadtime2 is the time between turning off G2 and turning on G1.

#### 11. Latch-up

#### Table 6.Latch-up

(Positive currents flow into pins)

| Symbol                | Parameter                                                   | Conditions | Min  | Unit |

|-----------------------|-------------------------------------------------------------|------------|------|------|

| I <sub>latch up</sub> | Latch-up current                                            | <u>[1]</u> |      |      |

|                       | Pin RS                                                      | <u>[1]</u> | -30  | mA   |

|                       | Pin CF                                                      | <u>[1]</u> | -50  | mA   |

|                       | Pin STOP                                                    | <u>[1]</u> | -80  | mA   |

|                       | Pins VO, OVC, CI, CP, EOL, RREF, STOP, S1, FS, G1, G2, GZCD | <u>[1]</u> | -100 | mA   |

Negative latch-up currents tested at T<sub>j</sub> = 150 °C by discharging a 22 mF capacitor through a 50 Ω series resistor. Positive latch-up currents according to quality specification.

# 12. Application information

## 12.1 Design equations

Equation 1 through Equation 5 give the design equations for the UBA2013:

| Table 7.         UBA2013 parameters (typical) |                    |

|-----------------------------------------------|--------------------|

| X1 = 3.24                                     | Rint = $3 k\Omega$ |

| t = 300ns                                     | Cpar = 5 pF (typ)  |

Bottom frequency fb is set by RREF and CF:

$$f_B = \frac{l}{2 \times \{[(C_{CF} + C_{par}) \times (Xl \times R_{RREF} - R_{int})] + \tau\}} (Hz)$$

(1)

Preheat time Tpreh is set by RREF and CP:

$$T_{preh} = 674 \times \frac{C_{CP}}{100 \, nF} \times \frac{R_{RREF}}{33 \, k\Omega} (ms)$$

(2)

Ignition time Tign is set by RREF and CP:

$$T_{ign} = 611 \times \frac{C_{CP}}{100nF} \times \frac{R_{RREF}}{33k\Omega} (ms)$$

(3)

Non-overlap time Tno is set by RREF:

$$T_{no} = 0.15 + 1.25 \times \frac{R_{RREF}}{33k\Omega}(\mu s)$$

PFC on-time Ton:

$$T_{ON}(V_{VO}) = T_{ON(max)} - \frac{(T_{ON(max)} - T_{ON(min)})}{\Delta V_{VO}} \times (V_{VO} - V_{VO(low)})$$

|     | -      | • |

|-----|--------|---|

| - 1 | 6      |   |

|     | : 1    |   |

|     | $\sim$ |   |

|     |        |   |

(4)

## **13. Test information**

The General Quality Specification for Integrated Circuits SNW-FQ-611-E is applicable.

## 14. Package outline

Fig 7. Package outline SOT109-1 (SO16)

NXP Semiconductors

-

# 16. Revision history

| Table 8. | <b>Revision histo</b> | ory                   |                      |               |            |

|----------|-----------------------|-----------------------|----------------------|---------------|------------|

| Documen  | t ID                  | Release date          | Data sheet status    | Change notice | Supersedes |

| UBA2013L | 1                     | <yyyymmdd></yyyymmdd> | Objective data sheet | -             | -          |

## 17. Legal information

## 17.1 Data sheet status

| NXP Semiconduo               | ctors                         | UBA2013/L3                                                                            |

|------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| 17. Legal infor              | rmation                       | HB driver IC                                                                          |

| 17.1 Data sheet              |                               | DRAKT DRAKT                                                                           |

| Document status[1][2]        | Product status <sup>[3]</sup> | Definition                                                                            |

| Objective [short] data sheet | Development                   | This document contains data from the objective specification for product development. |

Please consult the most recently issued document before initiating or completing a design [1]

The term 'short data sheet' is explained in section "Definitions" [2]

The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status [3] information is available on the Internet at URL http://www.nxp.com

#### 17.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### Disclaimers 17.3

General - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use - NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment nor in applications where failure or malfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications - Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values - Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale - NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, including those pertaining to warranty. intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

No offer to sell or license - Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### Licenses 17.4

#### Purchase of NXP <xxx> components

<License statement text>

## 17.5 Patents

Notice is herewith given that the subject device uses one or more of the following patents and that each of these patents may have corresponding patents in other jurisdictions.

<Patent ID> — owned by <Company name>

#### 17.6 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

<Name> — is a trademark of NXP B.V.

## 18. Contact information

For additional information, please visit: http://www.nxp.com For sales office addresses, send an email to: salesaddresses@nxp.com

## 19. Tables

| Table 1.<br>Table 2.<br>Table 3.<br>Table 4.<br>Table 5.<br>Table 6. | Ordering information         |

|----------------------------------------------------------------------|------------------------------|

| Table 7.<br>Table 8.                                                 | UBA2013 parameters (typical) |

|                                                                      |                              |

|                                                                      |                              |

|                                                                      |                              |

|                                                                      | G                            |

|                                                                      |                              |

|                                                                      |                              |

continued >>

TORACTORACTO

## 20. Figures

| Fig 1.<br>Fig 2.<br>Fig 3.<br>Fig 4.<br>Fig 5.<br>Fig 6.<br>Fig 7.<br>Fig 8. | Block diagram of UBA2013/L32Pin configuration for UBA2013/L33Oscillator timing4Excess charge control6PFC block9Application diagram of UBA2013L/314Package outline SOT109-1 (SO16)16State diagram and state transitions17 |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              |                                                                                                                                                                                                                          |

|                                                                              |                                                                                                                                                                                                                          |

continued >>

## 21. Contents

| 1    | General description 1                  |

|------|----------------------------------------|

| 2    | Features 1                             |

| 2.1  | Half bridge 1                          |

| 2.2  | PFC 1                                  |

| 3    | Applications 1                         |

| 4    | Ordering information 1                 |

| 5    | Block diagram 2                        |

| 6    | Pinning information 3                  |

| 6.1  | Pinning                                |

| 6.2  | Pin description                        |

| 7    | Functional description 4               |

| 7.1  | Start-up state                         |

| 7.2  | Half bridge oscillator                 |

| 7.3  | Oscillating state                      |

| 7.4  | Preheat state                          |

| 7.5  | Ignition state 5                       |

| 7.6  | Burn state 6                           |

| 7.7  | Capacitive mode protection             |

| 7.8  | Stop function                          |

| 7.9  | End-of-life protection7                |

| 7.10 | Non-oscillating state 7                |

| 7.11 | Start-up state                         |

| 7.12 | Stop state                             |

| 7.13 | VddLow state                           |

| 7.14 | PFC function                           |

| 7.15 | VO-low condition                       |

| 7.16 | State and transition diagrams          |

| 7.17 | Charge coupling                        |

| 8    | Limiting values 10                     |

| 9    | Thermal characteristics 11             |

| 10   | Characteristics                        |

| 11   | Latch-up 13                            |

| 12   | Application information                |

| 12.1 | Design equations 15                    |

| 13   | Test information 15                    |

| 14   | Package outline 16                     |

| 15   | Appendix 17                            |

| 15.1 | State diagram and state transitions 17 |

| 16   | Revision history 18                    |

| 17   | Legal information 19                   |

| 17.1 | Data sheet status 19                   |

| 17.2 | Definitions 19                         |

| 17.3 | Disclaimers                            |

| 17.4 | Licenses                               |

| 17.5 | Patents                                |

|      |                                        |

|      | O DALUIO, LO        |

|------|---------------------|

|      | HB driver IC        |

|      |                     |

|      |                     |

|      | Ra Ra Ra            |

|      |                     |

| 17.6 | Trademarks 19       |

| 18   | Contact information |

| 19   | Tables 20           |

| 20   | Figures             |

| 21   | Contents            |

UBA2013/

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2007.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 23 February 2007 Document identifier: UBA2013L\_1

All rights reserved.