Sample &

Buy

CSD18563Q5A

SLPS444C - JULY 2013-REVISED JANUARY 2016

# CSD18563Q5A 60 V N-Channel NexFET™ Power MOSFET

# 1 Features

- Ultra-Low Q<sub>g</sub> and Q<sub>gd</sub>

- Soft Body Diode for Reduced Ringing

- Low Thermal Resistance

- Avalanche Rated

- Logic Level

- Pb-Free Terminal Plating

- RoHS Compliant

- Halogen Free

- SON 5 mm × 6 mm Plastic Package

# 2 Applications

- Low-Side FET for Industrial Buck Converter

- Secondary Side Synchronous Rectifier

- Motor Control

## 3 Description

This 5.7 m $\Omega$ , 60 V SON 5 mm × 6 mm NexFET<sup>TM</sup> power MOSFET was designed to pair with the CSD18537NQ5A control FET and act as the sync FET for a complete industrial buck converter chipset solution.

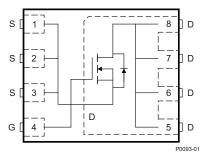

#### Top View

### **Product Summary**

| T <sub>A</sub> = 25° | c                             | TYPICAL VA             | UNIT |    |  |

|----------------------|-------------------------------|------------------------|------|----|--|

| V <sub>DS</sub>      | Drain-to-Source Voltage 60    |                        |      |    |  |

| Qg                   | Gate Charge Total (10 V)      | 15.0                   | nC   |    |  |

| Q <sub>gd</sub>      | Gate Charge Gate-to-Drain     | 2.9                    | nC   |    |  |

| Р                    | Drain-to-Source On-Resistance | $V_{GS} = 4.5 V$       | 8.6  | mΩ |  |

| R <sub>DS(on)</sub>  | Drain-to-Source On-Resistance | V <sub>GS</sub> = 10 V | 5.7  | mΩ |  |

| V <sub>GS(th)</sub>  | Threshold Voltage             | 2.0                    |      | V  |  |

### Ordering Information<sup>(1)</sup>

| DEVICE       | MEDIA                   | QTY | PACKAGE         | SHIP     |

|--------------|-------------------------|-----|-----------------|----------|

| CSD18563Q5A  | SD18563Q5A 13-Inch Reel |     | SON 5 × 6 mm    | Tape and |

| CSD18563Q5AT | 7-Inch Reel             | 250 | Plastic Package | Reel     |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Absolute Maximum Ratings**

| T <sub>A</sub> = 2                   | 5°C                                                                      | VALUE      | UNIT |

|--------------------------------------|--------------------------------------------------------------------------|------------|------|

| $V_{\text{DS}}$                      | Drain-to-Source Voltage                                                  | 60         | V    |

| $V_{GS}$                             | Gate-to-Source Voltage                                                   | ±20        | V    |

|                                      | Continuous Drain Current (Package limited)                               | 100        |      |

| ID                                   | Continuous Drain Current (Silicon limited), $T_C = 25^{\circ}C$          | 93         | А    |

|                                      | Continuous Drain Current <sup>(1)</sup>                                  | 15         |      |

| I <sub>DM</sub>                      | Pulsed Drain Current <sup>(2)</sup>                                      | 251        | А    |

| р                                    | Power Dissipation <sup>(1)</sup>                                         | 3.2        | W    |

| PD                                   | Power Dissipation, TC = 25°C                                             | 116        | vv   |

| T <sub>J</sub> ,<br>T <sub>stg</sub> | Operating Junction Temperature,<br>Storage Temperature                   | -55 to 150 | °    |

| E <sub>AS</sub>                      | Avalanche Energy, single pulse I_D = 54 A, L = 0.1 mH, R_G = 25 $\Omega$ | 146        | mJ   |

(1) Typical  $R_{\rm BJA}$  = 40°C/W on a 1 inch², 2 oz. Cu pad on a 0.06 inch thick FR4 PCB.

(2) Max  $R_{\theta JC}$  = 1.3°C/W, pulse duration ≤100 µs, duty cycle ≤1%.

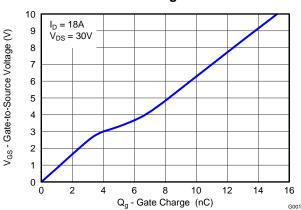

# Gate Charge

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

2

# Table of Contents

6.1 Community Resources......7 Features ..... 1 6.2 Trademarks ...... 7 Applications ..... 1 6.3 Description ..... 1 Revision History..... 2 7 Mechanical, Packaging, and Orderable Information ...... 8 Q5A Package Dimensions ...... 8 7.1 5.2 Thermal Information ...... 3 7.2 5.3 Typical MOSFET Characteristics ...... 4 7.3 Recommended Stencil Opening ...... 10 Device and Documentation Support......7 Q5A Tape and Reel Information ..... 10 7.4

## 4 Revision History

1

2

3

4

5

6

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision B (January 2015) to Revision C

| • | Added "Soft Body Diode for Reduced Ringing" under Features         | 1 |

|---|--------------------------------------------------------------------|---|

| • | Added "Low-Side FET for Industrial Buck Converter" to Applications | 1 |

| • | Updated the part description                                       | 1 |

| • | Added the Community Resources section                              | 7 |

#### Changes from Revision A (January 2014) to Revision B

| • | Increased silicon limited continuous drain current to 93 A               | 1 |

|---|--------------------------------------------------------------------------|---|

| • | Increased Pulsed Drain Current to 251                                    | 1 |

| • | Added line for max power dissipation with case temperature held to 25° C | 1 |

| • | Updated pulsed current conditions                                        | 1 |

| • | Changed Figure 1 to normalized R <sub>eJC</sub> curve                    | 4 |

|   | Updated SOA in Figure 10                                                 |   |

#### Changes from Original (July 2013) to Revision A

| • | Added more information to description                                                                                     | 1  |

|---|---------------------------------------------------------------------------------------------------------------------------|----|

| • | Added small reel order number                                                                                             | 1  |

| • | Removed T <sub>c</sub> = 25°C condition from continuous drain current (package limited) in Absolute Maximum Ratings table | 1  |

| • | Changed Typ R <sub>0JA</sub> = 99°C/W to: R <sub>0JA</sub> = 100°C/W in Figure 1                                          | 4  |

| • | Added the Recommended Stencil Opening section                                                                             | 10 |

|     | Texas       |

|-----|-------------|

| · Y | INSTRUMENTS |

www.ti.com

#### Page

#### Page

Page

## **5** Specifications

## 5.1 Electrical Characteristics

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

| <u> </u>            | PARAMETER                        | TEST CONDITIONS                                                                       | MIN | TYP  | MAX  | UNIT |

|---------------------|----------------------------------|---------------------------------------------------------------------------------------|-----|------|------|------|

| STATIC              | CHARACTERISTICS                  |                                                                                       |     |      |      |      |

| $BV_{DSS}$          | Drain-to-source voltage          | $V_{GS} = 0 V, I_D = 250 \mu A$                                                       | 60  |      |      | V    |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | $V_{GS} = 0 V, V_{DS} = 48 V$                                                         |     |      | 1    | μA   |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | $V_{DS} = 0 V, V_{GS} = 20 V$                                                         |     |      | 100  | nA   |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | $V_{DS} = V_{GS}$ , $I_D = 250 \ \mu A$                                               | 1.7 | 2.0  | 2.4  | V    |

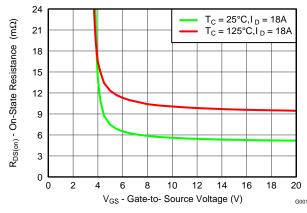

| D                   |                                  | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 18 A                                        |     | 8.6  | 10.8 | mΩ   |

| R <sub>DS(on)</sub> | Drain-to-source on resistance    | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 18 A                                         |     | 5.7  | 6.8  | mΩ   |

| 9 <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 30 V, I <sub>D</sub> = 18 A                                         |     | 60   |      | S    |

| DYNAMI              | C CHARACTERISTICS                |                                                                                       |     |      |      |      |

| C <sub>iss</sub>    | Input capacitance                |                                                                                       |     | 1150 | 1500 | pF   |

| C <sub>oss</sub>    | Output capacitance               | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 30 V, <i>f</i> = 1 MHz                       |     | 280  | 364  | pF   |

| C <sub>rss</sub>    | Reverse transfer capacitance     |                                                                                       |     | 3.9  | 5.1  | pF   |

| R <sub>G</sub>      | Series gate resistance           |                                                                                       |     | 1.5  | 3.0  | Ω    |

| Qg                  | Gate charge total (4.5 V)        |                                                                                       |     | 7.3  | 9.5  |      |

| Qg                  | Gate charge total (10 V)         |                                                                                       |     | 15   | 20   | nC   |

| Q <sub>gd</sub>     | Gate charge gate-to-drain        | V <sub>DS</sub> = 30 V, I <sub>D</sub> = 18 A                                         |     | 2.9  |      | nC   |

| Q <sub>gs</sub>     | Gate charge gate-to-source       |                                                                                       |     | 3.3  |      | nC   |

| Q <sub>g(th)</sub>  | Gate charge at V <sub>th</sub>   |                                                                                       |     | 2.3  |      | nC   |

| Q <sub>oss</sub>    | Output charge                    | V <sub>DS</sub> = 30 V, V <sub>GS</sub> = 0 V                                         |     | 36   |      | nC   |

| t <sub>d(on)</sub>  | Turn on delay time               |                                                                                       |     | 3.2  |      | ns   |

| t <sub>r</sub>      | Rise time                        |                                                                                       |     | 6.3  |      | ns   |

| t <sub>d(off)</sub> | Turn off delay time              | $V_{DS}$ = 30 V, V <sub>GS</sub> = 10 V, I <sub>DS</sub> = 18 A, R <sub>G</sub> = 0 Ω |     | 11.4 |      | ns   |

| t <sub>f</sub>      | Fall time                        |                                                                                       |     | 1.7  |      | ns   |

| DIODE C             | CHARACTERISTICS                  |                                                                                       |     |      |      |      |

| $V_{SD}$            | Diode forward voltage            | I <sub>SD</sub> = 18 A, V <sub>GS</sub> = 0 V                                         |     | 0.8  | 1    | V    |

| Q <sub>rr</sub>     | Reverse recovery charge          |                                                                                       |     | 63   |      | nC   |

| t <sub>rr</sub>     | Reverse recovery time            | $V_{DS}$ = 30 V, I <sub>F</sub> = 18 A, di/dt = 300 A/µs                              |     | 49   |      | ns   |

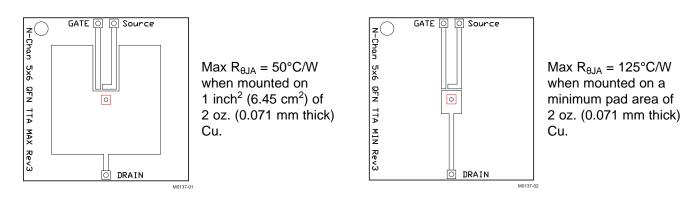

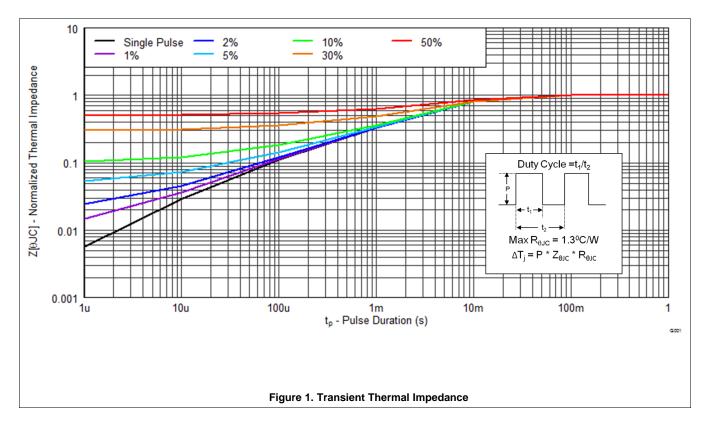

# 5.2 Thermal Information

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

|                 | THERMAL METRIC                                           | MIN | TYP | MAX | UNIT  |

|-----------------|----------------------------------------------------------|-----|-----|-----|-------|

| $R_{\theta JC}$ | Junction-to-case thermal resistance <sup>(1)</sup>       |     |     | 1.3 | °C/W  |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance <sup>(1)(2)</sup> |     |     | 50  | °C/VV |

$R_{\theta JC}$  is determined with the device mounted on a 1 inch<sup>2</sup> (6.45 cm<sup>2</sup>), 2 oz. (0.071 mm thick) Cu pad on a 1.5 inch x 1.5 inch (3.81 cm x 3.81 cm), 0.06 inch (1.52 mm) thick FR4 PCB.  $R_{\theta JC}$  is specified by design, whereas  $R_{\theta JA}$  is determined by the user's board design. Device mounted on FR4 material with 1 inch<sup>2</sup> (6.45 cm<sup>2</sup>), 2 oz. (0.071 mm thick) Cu. (1)

(2)

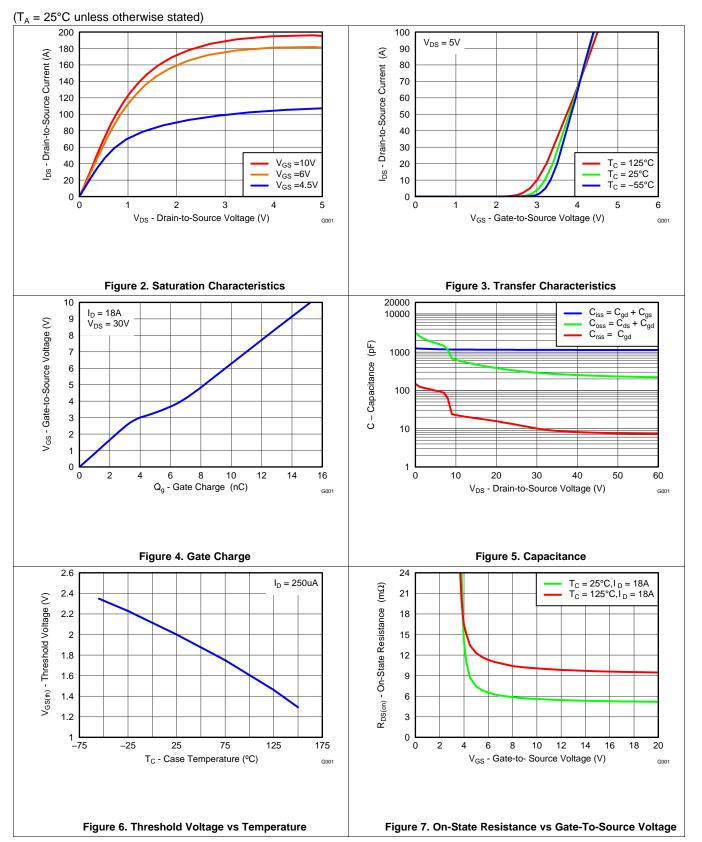

# 5.3 Typical MOSFET Characteristics

$(T_A = 25^{\circ}C \text{ unless otherwise stated})$

#### CSD18563Q5A SLPS444C – JULY 2013 – REVISED JANUARY 2016

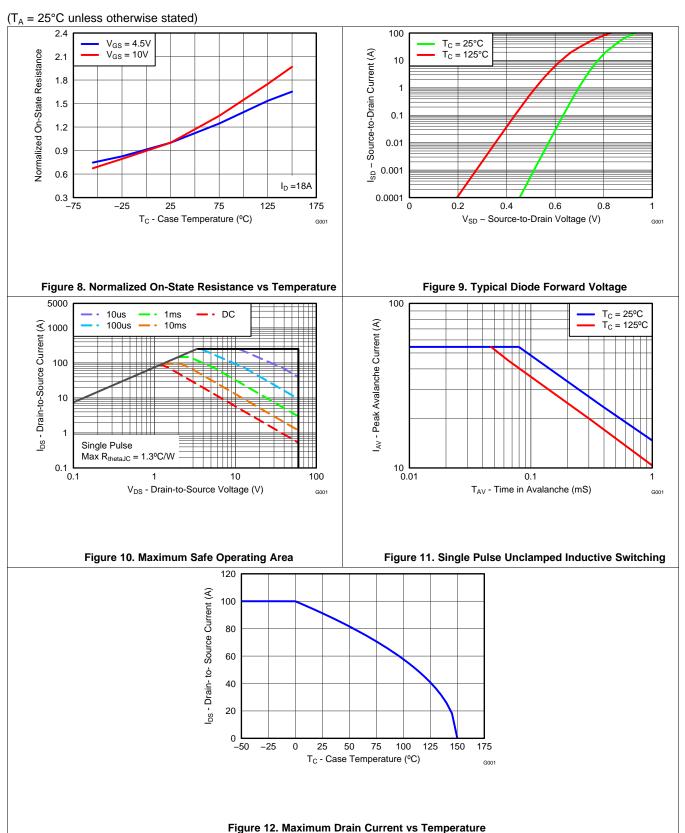

# **Typical MOSFET Characteristics (continued)**

# **Typical MOSFET Characteristics (continued)**

# 6 Device and Documentation Support

### 6.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 6.2 Trademarks

NexFET, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 6.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 6.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

Texas Instruments

www.ti.com

# 7 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

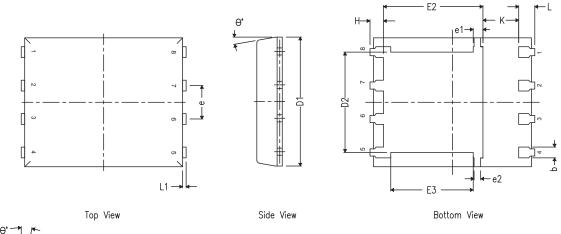

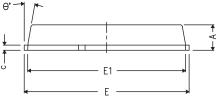

## 7.1 Q5A Package Dimensions

| DIM | MIL  | LIMETERS |      |

|-----|------|----------|------|

| DIM | MIN  | NOM      | MAX  |

| А   | 0.90 | 1.00     | 1.10 |

| b   | 0.33 | 0.41     | 0.51 |

| С   | 0.20 | 0.25     | 0.34 |

| D1  | 4.80 | 4.90     | 5.00 |

| D2  | 3.61 | 3.81     | 4.02 |

| E   | 5.90 | 6.00     | 6.10 |

| E1  | 5.70 | 5.75     | 5.80 |

| E2  | 3.38 | 3.58     | 3.78 |

| E3  | 3.03 | 3.13     | 3.23 |

| е   | 1.17 | 1.27     | 1.37 |

| e1  | 0.27 | 0.37     | 0.47 |

| e2  | 0.15 | 0.25     | 0.35 |

| Н   | 0.41 | 0.56     | 0.71 |

| К   | 1.10 |          |      |

| L   | 0.51 | 0.61     | 0.71 |

| L1  | 0.06 | 0.13     | 0.20 |

| θ   | 0°   |          | 12°  |

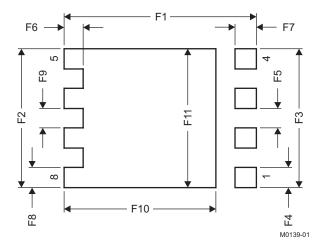

# 7.2 Recommended PCB Pattern

| DIM | MILLIMET | TERS  | INCH  | IES   |

|-----|----------|-------|-------|-------|

|     | MIN      | MAX   | MIN   | MAX   |

| F1  | 6.205    | 6.305 | 0.244 | 0.248 |

| F2  | 4.46     | 4.56  | 0.176 | 0.18  |

| F3  | 4.46     | 4.56  | 0.176 | 0.18  |

| F4  | 0.65     | 0.7   | 0.026 | 0.028 |

| F5  | 0.62     | 0.67  | 0.024 | 0.026 |

| F6  | 0.63     | 0.68  | 0.025 | 0.027 |

| F7  | 0.7      | 0.8   | 0.028 | 0.031 |

| F8  | 0.65     | 0.7   | 0.026 | 0.028 |

| F9  | 0.62     | 0.67  | 0.024 | 0.026 |

| F10 | 4.9      | 5     | 0.193 | 0.197 |

| F11 | 4.46     | 4.56  | 0.176 | 0.18  |

For recommended circuit layout for PCB designs, see application note SLPA005 – Reducing Ringing Through PCB Layout Techniques.

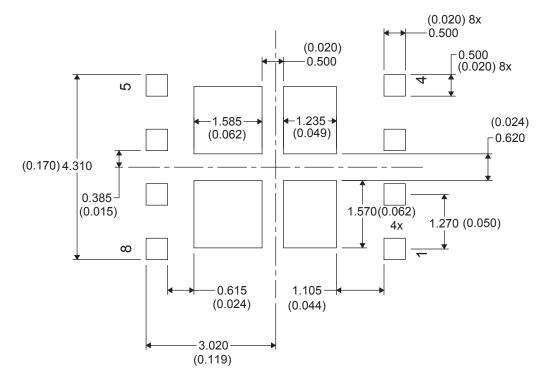

# 7.3 Recommended Stencil Opening

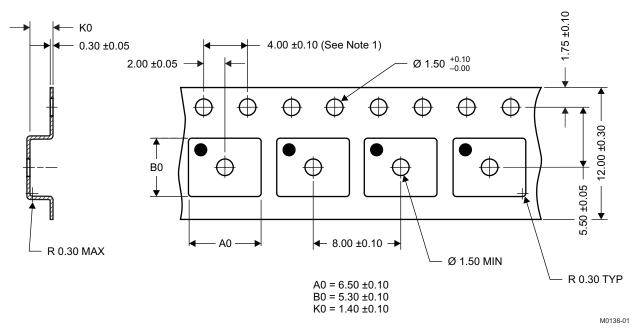

## 7.4 Q5A Tape and Reel Information

#### Notes:

- 1. 10-sprocket hole-pitch cumulative tolerance ±0.2

- 2. Camber not to exceed 1 mm in 100 mm, noncumulative over 250 mm

- 3. Material: black static-dissipative polystyrene

- 4. All dimensions are in mm (unless otherwise specified).

- 5. A0 and B0 measured on a plane 0.3 mm above the bottom of the pocket.

25-Apr-2017

# PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | •       | Pins | Package | Eco Plan                 | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|---------|--------------|---------|------|---------|--------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)     |              | Drawing |      | Qty     | (2)                      | (6)              | (3)                |              | (4/5)          |         |

| CSD18563Q5A      | ACTIVE  | VSONP        | DQJ     | 8    | 2500    | Pb-Free (RoHS<br>Exempt) | CU SN            | Level-1-260C-UNLIM | -55 to 150   | CSD18563       | Samples |

| CSD18563Q5A-P    | PREVIEW | VSONP        | DQJ     | 8    | 2500    | Pb-Free (RoHS<br>Exempt) | CU SN            | Level-1-260C-UNLIM | -55 to 150   | CSD18563       |         |

| CSD18563Q5AT     | ACTIVE  | VSONP        | DQJ     | 8    | 250     | Pb-Free (RoHS<br>Exempt) | CU SN            | Level-1-260C-UNLIM | -55 to 150   | CSD18563       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

25-Apr-2017

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated