#### Non-Isolated Buck APFC Offline LED Power Switch

#### **FEATURES**

- Active PFC for High PF and Low THD

- PF>0.9 with Universal Input

- Built-in HV Startup and IC Power Supply Circuit

- Internal 500V Power MOSFET

- Quasi-Resonant for High Efficiency

- ±1% CC Regulation

- Very Low VDD Operation Current

- Excellent Line and Load Regulation

- LED Open/Short Protection

- Build in Protections:

- Output Over Voltage Protection (OVP)

- Cycle-by-Cycle Current Limiting (OCP)

- Leading Edge Blanking (LEB)

- LED Open/Short Protection

- On-Chip Thermal Foldback (OTP)

- Available in SOP-7 Package

### **APPLICATIONS**

- LED Bulb Light/Ceiling Light

- LED T5/T8 Tube

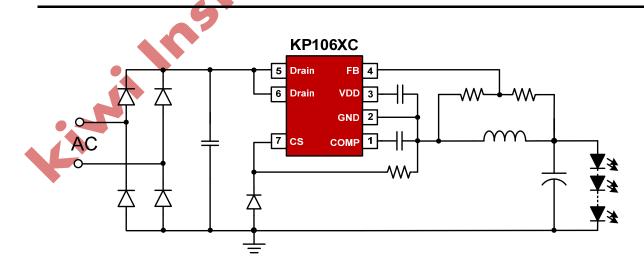

# TYPICAL APPLICATION CIRCUIT

#### GENERAL DESCRIPTION

KP106XC series are a highly integrated power switch with constant current (CC) control for LED lighting applications. The IC utilizes Quasi-Resonant (QR) Buck topology with active PFC control for high PF, low THD, and high efficiency.

KP106XC integrates 500V power MOSFET with high voltage startup and IC power supply circuit, which requires very few external components. The IC senses the inductor current during the whole switching cycle, which can achieve high precision CC control with excellent line and load regulation.

KP106XC integrates functions and protections of Under Voltage Lockout (UVLO), Cycle-by-cycle Current Limiting (OCP), Thermal Foldack (OTP), Output Over Voltage Protection (OVP), LED Open/Short Protection, etc.

Non-Isolated Buck APFC Offline LED Power Switch

## **Pin Configuration**

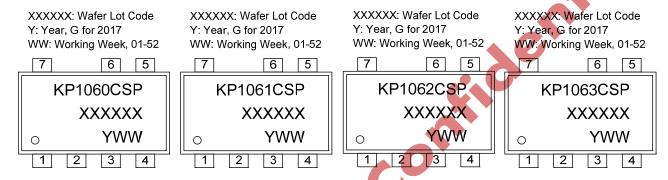

### **Marking Information**

SOP-7

### **Output Power Table**

| Part Number | Package  | Maximum Output Current (90-265Vac) |            |  |

|-------------|----------|------------------------------------|------------|--|

|             | . uonago | 36V output                         | 72V output |  |

| KP1060CSPA  | SOP-7    | 200 mA                             | 130 mA     |  |

| KP1061CSPA  | SOP-7    | 250 mA                             | 200 mA     |  |

| KP1062CSPA  | SOP-7    | 350 mA                             | 260 mA     |  |

| KP1063CSPA  | SOP-7    | 420 mA                             | 300 mA     |  |

**Note:** The system actual maximum output power is determined by the test.

## Pin Description

| Pin Number | Pin Name | I/O | Description                                                                             |

|------------|----------|-----|-----------------------------------------------------------------------------------------|

| X1         | COMP     | I   | Loop Compensation Pin. Connect a 1-4.7uF Ceramic Capacitor to GND Pin for CC regulation |

| 2          | GND      | Р   | IC Ground Pin                                                                           |

| 3          | VDD      | Р   | IC Power Supply Pin. Connect a >2.2uF Ceramic Capacitor to GND Pin                      |

| 4          | FB       | I   | This pin detects the inductor demagnetization signal and the output voltage             |

| 5,6        | Drain    | Р   | Internal Power MOSFET Drain Pin                                                         |

| 7          | CS       | I   | Current Sense Input Pin                                                                 |

Non-Isolated Buck APFC Offline LED Power Switch

# **Ordering Information**

| Part Number | Description                         |

|-------------|-------------------------------------|

| KP1060CSPA  | SOP-7, Pb free in T&R, 4000Pcs/Reel |

| KP1061CSPA  | SOP-7, Pb free in T&R, 4000Pcs/Reel |

| KP1062CSPA  | SOP-7, Pb free in T&R, 4000Pcs/Reel |

| KP1063CSPA  | SOP-7, Pb free in T&R, 4000Pcs/Reel |

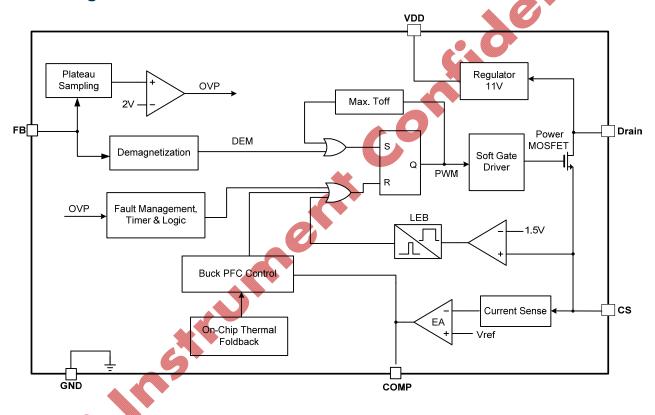

### **Block Diagram**

Non-Isolated Buck APFC Offline LED Power Switch

# **Absolute Maximum Ratings (Note 1)**

| Parameter                                             | Value       | Unit |

|-------------------------------------------------------|-------------|------|

| Drain Pin Voltage Range                               | -0.3 to 500 | V    |

| VDD DC Supply Voltage                                 | 14          | V    |

| VDD DC Clamp Current                                  | 10          | mA   |

| CS, FB, COMP Voltage Range                            | -0.3 to 7   | V    |

| Package Thermal ResistanceJunction to Ambient (SOP-7) | 165         | °C/W |

| Maximum Junction Temperature                          | 150         | °C   |

| Storage Temperature Range                             | -65 to 150  | °C   |

| Lead Temperature (Soldering, 10sec.)                  | 260         | °C   |

| ESD Capability, HBM (Human Body Model)                | 3           | kV   |

| ESD Capability, MM (Machine Model)                    | 250         | V    |

# **Recommended Operation Conditions (Note 2)**

| Parameter                     | <br>Value  | Unit |

|-------------------------------|------------|------|

| Operating Ambient Temperature | -40 to 125 | °C   |

# Electrical Characteristics (Ta = 25°C, VDD=11V, if not otherwise noted)

| Symbol                    | Parameter                               | Test Conditions            | Min | Тур. | Max | Unit |  |

|---------------------------|-----------------------------------------|----------------------------|-----|------|-----|------|--|

| Supply Volta              | Supply Voltage Section(VDD Pin)         |                            |     |      |     |      |  |

| I <sub>VDD_st</sub>       | Start-up current into VDD pin           | VDD <v<sub>DD_Op</v<sub>   |     | 300  | 700 | uA   |  |

| I <sub>VDD_Op</sub>       | Operation Current                       | Fsw=7KHz                   | 80  | 150  | 300 | uA   |  |

| V <sub>DD_Op</sub>        | VDD Operation Voltage                   |                            | 10  | 11.5 | 13  | V    |  |

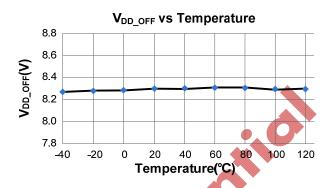

| $V_{DD\_OFF}$             | VDD Under Voltage Lockout<br>Enter      |                            | 7   | 8    | 9   | V    |  |

| V <sub>DD_Clamp</sub>     | VDD Zener Clamp Voltage                 | $I(V_{DD}) = 5 \text{ mA}$ |     | 14   |     | V    |  |

| Feedback Section (FB Pin) |                                         |                            |     |      |     |      |  |

| V <sub>FB_DEM</sub>       | Demagnetization Comparator Threshold    | (Note 3)                   |     | 0.2  |     | V    |  |

| $V_{FB\_OVP}$             | Over Voltage Protection (OVP) Threshold |                            | 1.9 | 2    | 2.1 | V    |  |

| $T_{off\_min}$            | Minimum OFF time                        | (Note 3)                   |     | 2    |     | us   |  |

Non-Isolated Buck APFC Offline LED Power Switch

|                      | T                                              |             | T   |     | 1   | I   |

|----------------------|------------------------------------------------|-------------|-----|-----|-----|-----|

| T <sub>on_max</sub>  | Maximum ON time                                | (Note 3)    |     | 40  |     | us  |

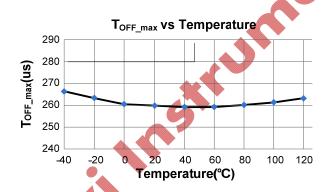

| T <sub>off_max</sub> | Maximum OFF time                               |             | 195 | 270 | 350 | us  |

| F <sub>max</sub>     | Max. Switching Frequency                       |             |     | 100 |     | KHz |

| Current Sen          | se Input Section (CS Pin)                      |             |     |     |     |     |

| T <sub>LEB</sub>     | OCP Leading Edge Blanking<br>Time              |             |     | 300 |     | ns  |

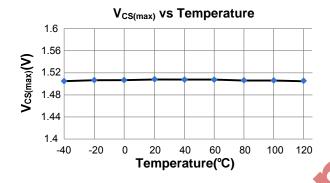

| $V_{cs(max)}$        | Current limiting threshold                     |             | 1.4 | 1.5 | 1.6 | V   |

| T <sub>D_OC</sub>    | Over Current Detection and Control Delay       |             |     | 100 |     | ns  |

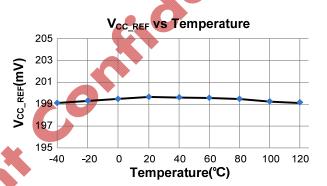

| V <sub>CC_REF</sub>  | Internal Reference for CC Loop Regulation      |             | 194 | 200 | 206 | mV  |

| CC Loop Co           | mpensation Section (COMP Pi                    | in)         |     |     |     |     |

| V <sub>comp_H</sub>  | COMP High Clamp Voltage                        |             |     | 3   |     | V   |

| V <sub>comp_L</sub>  | COMP Low Clamp Voltage                         |             |     | 0.7 |     | V   |

| Over Tempe           | rature Protection                              | <b>~</b> O' |     |     |     |     |

| T <sub>SD</sub>      | Thermal Foldback Trigger<br>Point              | (Note 3)    |     | 150 |     | °C  |

| HV Startup a         | and IC Supply Section (Drain P                 | Pin)        |     |     |     |     |

| I <sub>HV</sub>      | HV Charging Current                            | Drain =20V  |     | 10  |     | mA  |

| I <sub>HV_leak</sub> | Leakage Current of HV<br>Charging Circuit      |             | 10  | 40  | 60  | uA  |

| Power MOS            | FET Section (Drain Pin)                        |             |     |     |     |     |

| V <sub>BR</sub>      | Power MOSFET Drain<br>Source Breakdown Voltage |             | 500 |     |     | V   |

|                      |                                                | KP1060C     |     | 8.5 |     | Ω   |

| Б                    | Static Drain-Source On                         | KP1061C     |     | 5.3 |     | Ω   |

| R <sub>dson</sub>    | Resistance                                     | KP1062C     |     | 2.5 |     | Ω   |

|                      |                                                | KP1063C     |     | 1.9 |     | Ω   |

**Note 1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. The device is not guaranteed to function outside its operating conditions.

Note 3. Guaranteed by the Design.

Non-Isolated Buck APFC Offline LED Power Switch

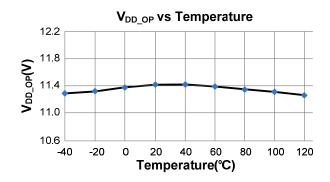

#### **Characterization Plots**

Non-Isolated Buck APFC Offline LED Power Switch

### **Operation Description**

KP106XC series are a highly integrated power switch with constant current (CC) control for LED lighting applications. The IC utilizes Quasi-Resonant (QR) Buck topology with active PFC control for high PF, low THD, and high efficiency.

#### 11V Regulator

In KP106XC, the 11V regulator charges VDD hold-up capacitor to 11V by drawing a current from the voltage on the Drain pin, whenever the internal power MOSFET is off. When the power MOSFET is on, the charging device runs off of the energy stored in the VDD hold-up capacitor. Extremely low IC power consumption allows KP106XC to operate continuously from the current drawn from the Drain pin. A capacitor value about 2.2uF is sufficient for both high frequency decoupling and energy storage.

#### System Start-Up Operation

After system power up, VDD hold up capacitor is charged by the internal HV startup circuit through Drain pin. When VDD pin voltage reaches the turn on threshold, the IC begins working. The COMP pin is pulled up to 0.7V quickly, then the IC begins to work at low switching frequency (typical 3.5KHz), the COMP pin voltage rises up gradually, thus the inductor peak current also rises up. The LED current hence achieves a soft start without over shoot.

#### Constant Current (CC) Control

kP106XC adopts floating ground structure. The inductor current is sensed during the whole switching cycle. The IC can accurately control the output current by the internal current feedback control loop. The output mean current in constant current (CC) mode can be expressed as:

$$I_{CC\_OUT} (mA) = \frac{V_{CC\_REF}}{R_{CS}} = \frac{200mV}{Rcs(\Omega)}$$

In the equation above,

Rcs--- the sensing resistor connected between CS and GND.

#### Leading Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs across the sensing resistor. The spike is caused by primary side capacitance and secondary side rectifier reverse recovery. To avoid premature termination of the switching pulse, an internal leading edge blanking circuit is built in. During this blanking period (300ns, typical), the PWM comparator is disabled and cannot switch off the gate driver.

#### Demagnetization Detection

KP106XC senses the output current zero crossing information through the external resistor feedback network. If FB pin voltage drops below 0.2V, an internal DEM comparator is triggered and a new switching cycle is initiated following the DEM triggering. The power MOSFET is always turned on with zero inductor current such that the turn-on loss and noise can be minimized.

#### Minimum and Maximum OFF Time

In KP106XC, a minimum OFF time (typically 2us) is implemented to suppress ringing when the power MOSFET is off. The minimum OFF time is necessary in applications where the transformer has a large leakage inductance. The maximum OFF time in KP106XC is typically 270us.

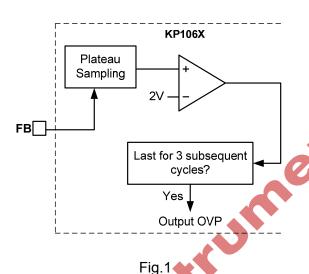

#### Output Over Voltage Protection (OVP)

Non-Isolated Buck APFC Offline LED Power Switch

In KP106XC, the output OVP is integrated by plateau sampling the auxiliary winding in the PWM OFF state. If the sampled plateau voltage exceeds the OVP threshold (2V), an internal counter starts counting subsequent OVP events. If OVP events are detected in successive 3 cycles, the controller assumes a true OVP and it stops all switching operations, as shown in Fig.1. The counter has been added to prevent incorrect OVP detection which might occur during ESD or lightning events. If the output voltage exceeds the OVP threshold less than 3 successive cycles, the internal counter will be cleared and no fault is asserted. Output OVP is auto-recovery mode protection.

Auto-Restart Protection

In the event of LED open loop condition/output OVP protection, the IC enters into auto-restart and VDD oscillation mode begins, wherein the power MOSFET is disabled. In VDD oscillation mode, the VDD hold-up capacitor voltage will periodically ramp up and down between 11.5V and 8.3V with a digital counter counting the oscillation cycle. When 8 cycles had been counted, the IC will reset and start up the system again. However, if the fault still exists, the system will experience the above mentioned process. If the fault has gone,

the system will resume normal operation.

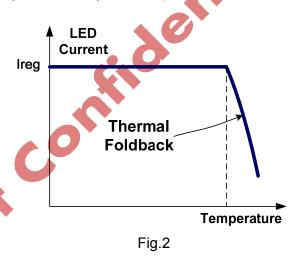

#### On Chip Thermal Foldback (OTP)

KP106XC integrates thermal foldback function. When the IC temperature is over 150 °C, the system output regulation current is gradually reduced, as shown in Fig.2. Thus, the output power and thermal dissipation are also reduced. In this way, the system temperature is limited and system reliability is also improved.

Soft Totem-Pole Gate Driver

KP106XC has a soft totem-pole gate driver with optimized EMI performance.

Non-Isolated Buck APFC Offline LED Power Switch

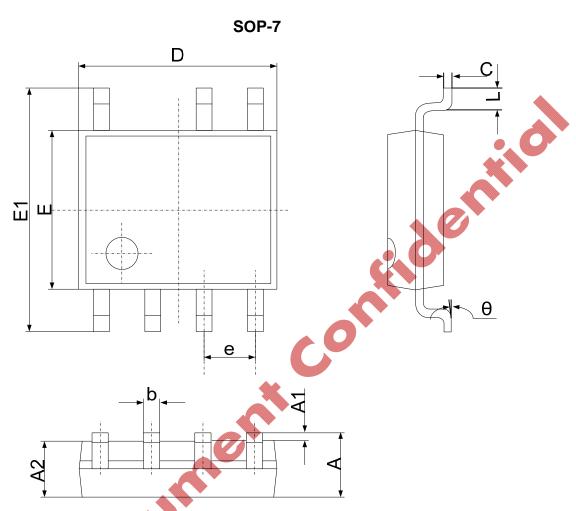

# **Package Dimension**

| Symbol | Dimensions in Millimeters |       | Dimensions | in Inches |  |

|--------|---------------------------|-------|------------|-----------|--|

|        | Min                       | Max   | Min        | Max       |  |

| Α      | 1.350                     | 1.750 | 0.053      | 0.069     |  |

| A1     | 0.100                     | 0.250 | 0.004      | 0.010     |  |

| A2     | 1.350                     | 1.550 | 0.053      | 0.061     |  |

| b      | 0.330                     | 0.510 | 0.013      | 0.020     |  |

| C      | 0.170                     | 0.250 | 0.006      | 0.010     |  |

| D      | 4.700                     | 5.100 | 0.185      | 0.200     |  |

| E      | 3.800                     | 4.000 | 0.150      | 0.157     |  |

| E1     | 5.800                     | 6.200 | 0.228      | 0.244     |  |

| е      | 1.270 (BSC)               |       | 0.050 (    | BSC)      |  |

| L      | 0.400                     | 1.270 | 0.016      | 0.050     |  |

| θ      | 0°                        | 8°    | 0°         | 8°        |  |

Non-Isolated Buck APFC Offline LED Power Switch

### **Revision History**

| DATE                                                                 | REV. | DI                                                                             | ESCRIPTION                             |  |  |

|----------------------------------------------------------------------|------|--------------------------------------------------------------------------------|----------------------------------------|--|--|

| 2016/05/10                                                           | 1.0  | First Release                                                                  |                                        |  |  |

| 2016/06/24                                                           | 1.01 | Update Characterization Plots, VDD_ON: VDD_OP     2,Update address of HangZhou |                                        |  |  |

| 2016/08/16                                                           | 1.1  | Upda                                                                           | ite the EC Table                       |  |  |

| 2016/10/13                                                           | 1.11 | The recommended value of                                                       | the VDD capacitor is updated to 2.2 uF |  |  |

| 2016/12/16                                                           | 1.2  | Part Number                                                                    | KP1060CSPA is added                    |  |  |

| 2017/02/13                                                           | 1.3  | Update (                                                                       | Ordering Information                   |  |  |

| 2017/04/05                                                           | 1.4  | Update the                                                                     | e Output power table                   |  |  |

| 2017/08/04                                                           | 1.5  | Up                                                                             | odate EC table                         |  |  |

| Contact Us:  US  (Hangzhou  (R&D Contact)  (Marketing/Field Support) |      |                                                                                |                                        |  |  |

| Contact Us:                                                          |      |                                                                                |                                        |  |  |

| US (Headquarter):                                                    |      | Hangzhou<br>(R&D Center):                                                      | Shenzhen (Marketing/Field Support):    |  |  |

#### **Contact Us:**

Add: 2060 Walsh Ave, Suite 244, Santa Clara, CA, 95050

Tel: 1-408-475-6888 Fax: 1-408-905-6912

E-mail: marketing@kiwiinst.com

Add: Room 1201, Building C, No.581 HuoJu Rd., Binjiang Dist., Hangzhou,

P.R.C

Tel: (86) 571-8795-8612 Fax: (86) 571-8795-5363

E-mail: marketing@kiwiinst.com.cn

Add: B302-B303, University Creative Park, Xili Rd., Nanshan

Dist., Shenzhen, P.R.C Tel: (86)755-8204-2689 Fax: (86)755-8204-2192

E-mail: marketing@kiwiinst.com.cn

#### **Disclaimer**

Information that is provided by Kiwi Instruments Corporation is believed to be accurate and reliable. Kiwi instrument reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Kiwi instrument products into any application. No legal responsibility for any said applications is assumed by Kiwi Instrument.