# 14-BIT REGISTERED BUFFER WITH SSTL I/O

#### IDT74SSTV16857

#### **FEATURES:**

- · 2.3V to 2.7V Operation

- · SSTL\_2 Class II style data inputs/outputs

- · Differential CLK input

- RESET control compatible with LVCMOS levels

- · Flow-through architecture for optimum PCB design

- Drive up to equivalent of 14 SDRAM loads

- · Latch-up performance exceeds 100mA

- ESD >2000V per MIL-STD-883, Method 3015; >200V using machine model (C = 200pF, R = 0)

- · Available in TSSOP package

#### **APPLICATIONS:**

Ideally suited for DIMM DDR registered applications

### **DESCRIPTION:**

The SSTV16857 is a 14-bit registered buffer designed for 2.3V-2.7V VDD and supports low standby operation. All data inputs and outputs are SSTL\_2 level compatible with JEDEC standard for SSTL\_2.

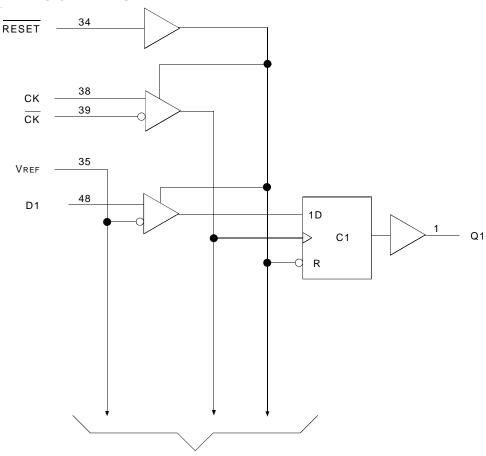

RESET is an LVCMOS input since it must operate predictably during the power-up phase. RESET, which can be operated independent of CLK and CLK, must be held in the low state during power-up in order to ensure predictable outputs (low state) before a stable clock has been applied.

RESET, when in the low state, will disable all input receivers, reset all registers, and force all outputs to a low state, before a stable clock has been applied. With inputs held low and a stable clock applied, outputs will remain low during the Low-to-High transition of RESET.

#### FUNCTIONAL BLOCK DIAGRAM

TO 13 OTHER CHANNELS

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

MAY 2003

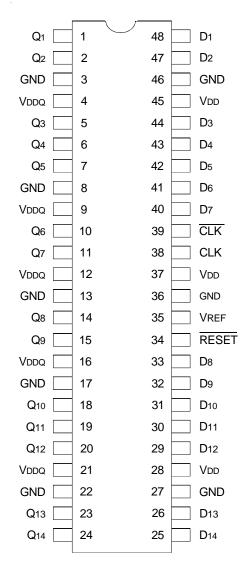

#### **PIN CONFIGURATION**

TSSOP TOP VIEW

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol            | Description                          | Max.             | Unit |

|-------------------|--------------------------------------|------------------|------|

| VDD or VDDQ       | Supply Voltage Range                 | -0.5 to 3.6      | V    |

| VI <sup>(2)</sup> | Input Voltage Range -0.5 to VDD +0.5 |                  | V    |

| Vo <sup>(3)</sup> | Output Voltage Range                 | -0.5 to VDDQ+0.5 | V    |

| lık               | Input Clamp Current, Vi < 0          | -50              | mA   |

| Іок               | Output Clamp Current,                | ±50              | mA   |

|                   | Vo < 0 or $Vo > VDDQ$                |                  |      |

| lo                | Continuous Output Current,           | ±50              | mA   |

|                   | Vo = 0 to $VDDQ$                     |                  |      |

| Vdd               | Continuous Current through each      | ±100             | mA   |

|                   | VDD, VDDQ or GND                     |                  |      |

| Tstg              | Storage Temperature Range            | -65 to +150      | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- 2. The input and output negative voltage ratings may be exceeded if the ratings of the I/P and O/P clamp current are observed.

- 3. The output current will flow if the following conditions are observed:

- a) Output in HIGH state

- b) Vo = VDDQ

### FUNCTION TABLE(1)

| RESET | CLK      | CLK           | D | Q Outputs        |

|-------|----------|---------------|---|------------------|

| Н     | <b>↑</b> | $\rightarrow$ | L | L                |

| Н     | <b>↑</b> | <b>→</b>      | Н | Н                |

| Н     | L or H   | L or H        | Х | Q <sup>(2)</sup> |

| L     | Х        | Χ             | Х | L                |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- ↑ = LOW to HIGH

- ↓ = HIGH to LOW

- 2. Q = Output level before the indicated steady-state conditions were established.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = -40°C to +85°C, VDD =  $2.5V \pm 0.2V$ , VDDQ =  $2.5V \pm 0.2V$

| Symbol | Parameter                      | Test Conditions                                                                     | Min.      | Тур. | Max. | Unit     |  |

|--------|--------------------------------|-------------------------------------------------------------------------------------|-----------|------|------|----------|--|

| Vik    | Control Inputs                 | Inputs VDD = 2.3V, II = -18mA                                                       |           | _    | -1.2 | V        |  |

| Vон    |                                | V <sub>DD</sub> = 2.3V to 2.7V, I <sub>OH</sub> = -100μA                            | VDD - 0.2 | _    | _    | V        |  |

|        |                                | V <sub>DD</sub> = 2.3V, IOH = -16mA                                                 | 1.95      | _    | _    |          |  |

| Vol    |                                | $V_{DD} = 2.3V \text{ to } 2.7V, \text{ IoL} = 100 \mu\text{A}$                     | _         | _    | 0.2  | V        |  |

|        |                                | V <sub>DD</sub> = 2.3V, I <sub>OL</sub> = 16mA                                      | _         | _    | 0.35 |          |  |

| lı     | All Inputs                     | VDD = 2.7V, VI = VDD or GND                                                         | _         | _    | ±5   | μА       |  |

| Idd    | Static Standby                 | Io = 0, Vdd = 2.7V, RESET = GND                                                     | _         | _    | 0.01 | mA       |  |

|        | Static Operating               | IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC)                          |           | _    | _    |          |  |

| Iddd   | Dynamic Operating (Clock Only) | $IO = 0$ , $VDD = 2.7V$ , $\overline{RESET} = VDD$ , $VI = VIH$ (AC) or $VIL$ (AC), | _         | _    | _    | μΑ/Clock |  |

|        |                                | CLK and CLK Switching 50% Duty Cycle.                                               |           |      |      | MHz      |  |

|        | Dynamic Operating              | IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC),                         | _         | _    | _    | μΑ/Clock |  |

|        | (Per Each Data Input)          | CLK and CLK Switching 50% Duty Cycle. One Data Input                                |           |      |      | MHz/Data |  |

|        |                                | Switching at Half Clock Frequency, 50% Duty Cycle.                                  |           |      |      | Input    |  |

| rон    | Output HIGH                    | V <sub>DD</sub> = 2.3V to 2.7V, I <sub>OH</sub> = -20mA                             | 7         | _    | 20   | Ω        |  |

| rol    | Output LOW                     | V <sub>DD</sub> = 2.3V to 2.7V, I <sub>OH</sub> = 20mA                              | 7         | _    | 20   | Ω        |  |

| ΓO(Δ)  | rон-rоц each separate bit      | V <sub>DD</sub> = 2.5V, T <sub>A</sub> = 25°C, I <sub>OH</sub> = -20mA              | _         | _    | 4    | Ω        |  |

|        | Data Inputs                    | $VDD = 2.5V$ , $VI = VREF \pm 310mV$                                                | 2.5       | _    | 3.5  |          |  |

| Сі     | CLK and CLK                    | VICR = 1.25V, VI (PP) = 360mV                                                       | 2.5       |      | 3.5  | pF       |  |

|        | RESET                          | VI = VDD or GND                                                                     | _         |      | 1    |          |  |

## OPERATING CHARACTERISTICS, TA = 25°C(1)

| Symbol | Parameter                        |             | Min.        | Тур. | Max.       | Unit |

|--------|----------------------------------|-------------|-------------|------|------------|------|

| Vdd    | Supply Voltage                   |             | VDDQ        | _    | 2.7        | V    |

| VDDQ   | Output Supply Voltage            |             | 2.3         | 2.5  | 2.7        | V    |

| Vref   | Reference Voltage (VREF= VDDQ/2) |             | 1.15        | 1.25 | 1.35       | V    |

| VTT    | Termination Voltage              |             | VREF- 40mV  | Vref | VREF+ 40mV | V    |

| Vı     | Input Voltage                    |             | 0           | _    | VDD        | V    |

| ViH    | AC High-Level Input Voltage      | Data Inputs | VREF+ 310mV | _    | _          | V    |

| VIL    | AC Low-Level Input Voltage       | Data Inputs | _           | _    | VREF-310mV | V    |

| VIH    | DC High-Level Input Voltage      | Data Inputs | VREF+ 150mV | _    | _          | V    |

| VIL    | DC Low-Level Input Voltage       | Data Inputs | _           | _    | VREF-150mV | V    |

| Vih    | High-Level Input Voltage         | RESET       | 1.7         | _    | _          | V    |

| VIL    | Low-Level Input Voltage          | RESET       | _           | _    | 0.7        | V    |

| Vicr   | Common-Mode Input Range          | CLK, CLK    | 0.97        | _    | 1.53       | V    |

| VI(PP) | Peak-to-Peak Input Voltage       | CLK, CLK    | 360         | _    | _          | mV   |

| Іон    | High-Level Output Current        |             | _           | _    | -20        | mA   |

| loL    | Low-Level Output Current         |             | _           | _    | 20         |      |

| TA     | Operating Free-Air Temperature   |             | -40         | _    | +85        | °C   |

#### NOTE:

<sup>1.</sup> The  $\overline{\text{RESET}}$  input of the device must be held at VDD or GND to ensure proper device operation.

# TIMING REQUIREMENTS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE

|        |                                                  |                        | $V_{DD} = 2.5V \pm 0.2V$ |      |      |

|--------|--------------------------------------------------|------------------------|--------------------------|------|------|

| Symbol | Parameter                                        |                        | Min.                     | Max. | Unit |

| CLOCK  | Clock Frequency                                  |                        | _                        | 200  | MHz  |

| tw     | Pulse Duration, CLK, CLK HIGH or LOW             |                        | 2.5                      | _    | ns   |

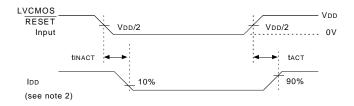

| tact   | Differential Inputs Active Time <sup>(1)</sup>   |                        | _                        | 22   | ns   |

| tinact | Differential Inputs Inactive Time <sup>(2)</sup> |                        | _                        | 22   | ns   |

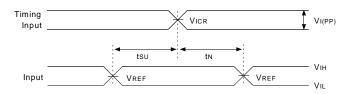

| tsu    | Setup Time, Fast Slew Rate <sup>(3,5)</sup>      | Data Before CLK↑, CLK↓ | 0.75                     | _    | ns   |

|        | Setup Time, Slow Slew Rate(4,5)                  |                        | 0.9                      | _    | ns   |

| tN     | Hold Time, Fast Slew Rate(3,5)                   | Data Before CLK↑, CLK↓ | 0.75                     | _    | ns   |

|        | Hold Time, Slow Slew Rate <sup>(2,5)</sup>       |                        | 0.9                      | _    | ns   |

#### NOTES:

- 1. Data inputs must be low a minimum time of tact max., after RESET is taken HIGH.

- 2. Data and clock inputs must be held at valid levels (not floating) a minimum time of tinact max., after RESET is taken LOW.

- 3. For data signal input slew rate is  $\geq 1V/ns$ .

- 4. For data signal input slew rate is ≥0.5V/ns and <1V/ns.

- 5. CLK, CLK signal input slew rates are ≥1V/ns.

# SWITCHING CHARACTERISTICS OVER RECOMMENDED FREE-AIR OPERATING RANGE (UNLESS OTHERWISE NOTED)

|         |                  | $VDD = 2.5V \pm 0.2V$ |      |      |

|---------|------------------|-----------------------|------|------|

| Symbol  | Parameter        | Min                   | Max. | Unit |

| fMAX    |                  | 200                   | _    | MHz  |

| tpD tpD | CLK and CLK to Q | 1.1                   | 2.8  | ns   |

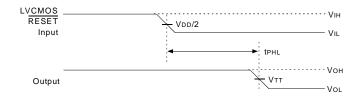

| tphl.   | RESET to Q       | _                     | 5    | ns   |

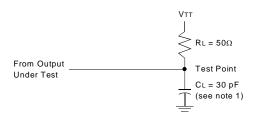

## TEST CIRCUITS AND WAVEFORMS (VDD = 2.5V ± 0.2V)

Load Circuit

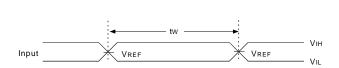

Voltage and Current Waveforms Inputs Active and Inactive Times

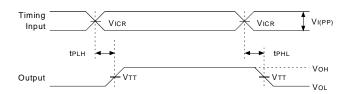

Voltage Waveforms - Propagation Delay Times

Voltage Waveforms - Pulse Duration

Voltage Waveforms - Propagation Delay Times

Voltage Waveforms - Setup and Hold Times

#### NOTES:

- 1. CL includes probe and jig capacitance.

- 2. IDD tested with clock and data inputs held at VDD or GND, and Io = 0mA.

- 3. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 10MHz, Zo = 50 $\Omega$ , input slew rate = 1 V/ns  $\pm$ 20% (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- 5. VTT = VREF = VDDQ/2

- 6. VIH = VREF + 310mV (AC voltage levels) for differential inputs. VIH = VDD for LVCMOS input.

- VIL = VREF 310mV (AC voltage levels) for differential inputs. VIL = GND for LVCMOS input.

- 8. tplh and tphL are the same as tpd.

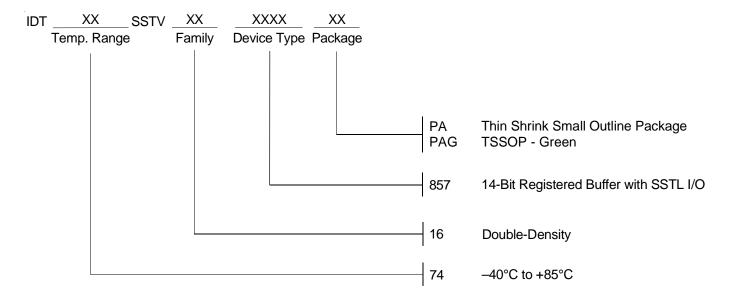

## ORDERING INFORMATION

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com

for Tech Support: logichelp@idt.com (408) 654-6459