# EG4X20-MINI-DEV 使用说明

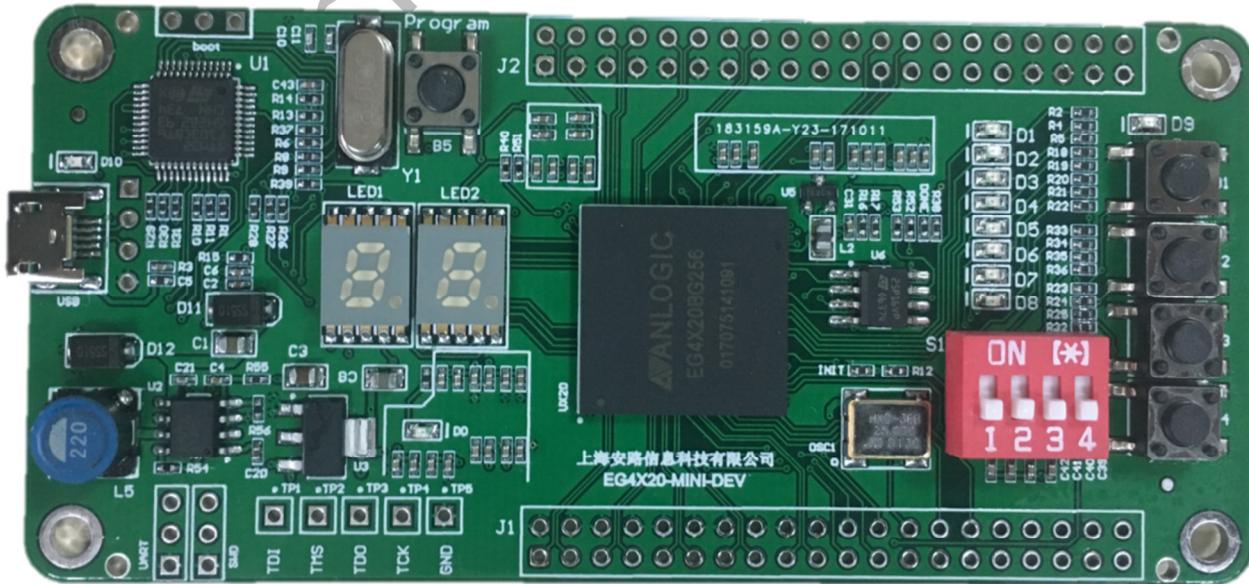

## 一、 EG4X20-MINI-DEV 开发板简介

1. 开发板可以由 micro USB 5V 供电 ,板载下载器可以支持 FPGA 下载、调试、烧录 flash 等功能。

2. FPGA IO 电压为 3.3V , 内核电压为 1.2V。

3. 两位带点动态数码管显示。

4. 八路 LED 指示灯。

5. 四个按键输入。

6. 一个四位拨码开关。

7. 一个 program 按键。

8. 板级 25M 有源晶振。

9. 一个 SD 卡座。

10. FPGA 配置 flash 六线接 FPGA。

11. 两排 GPIO 口 , 其中包含 :

- 10 对 TRUE LVDS 输入输出 , 包含有 GCLK 差分管脚。

- 4 路 ADC 采样通道。

EG4X20-MINI-DEV FPGA 开发板专为安路 EAGLE 系列 EG4X20BG256 芯片设计，为客户做芯片评估、提供参考设计。开发板集合了下载器模块，用户正常使用过程中只需用一条 micro USB 线接到电脑，即可对开发板供电、更新代码设计。开发板长 10cm、宽 4.8cm，板上集成了 2 位数码管显示、8 路 LED 灯、4 路拨码开关、4 位可编程按键、25M 有源晶振、9 对 TRUE LVDS 差分对、4 路 ADC 采样通道、一个 SDCARD 接口（背面不焊），最多 92 个 IO 可用，板上能为客户做各种交互设计，板上的 GPIO 口可为客户提供接口拓展，为客户接更多外设提供方便。

开发板包装清单包含：

- a) 开发板一块；

- b) 铜柱 4 个；

- c) micro USB 线一条；

开发板配套的开发软件、参考电路、参考例程可在百度网盘下载，软件版本会提供更新，

下载链接：

链接：<http://pan.baidu.com/s/1bzNTro> 密码：a7w9 包含了开发板原理图。

## 二、 开发板下载驱动安装

1. 安装 TD 软件；

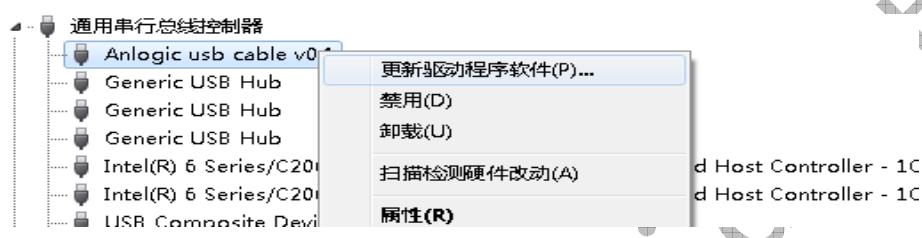

2. 开发板通过 micro USB(安卓)线连到电脑，右键 “计算机->设备管理器”，在弹出的新设备中点右键选择 “更新驱动程序软件”，在弹出的选项中点击 “浏览计算机以查找驱动程序软件”

- 自动搜索更新的驱动程序软件(S)

Windows 将在您的计算机和 Internet 上查找用于相关设备的最新驱动程序软件，除非在设备安装设备中禁用该功能。

- 浏览计算机以查找驱动程序软件(R)

手动查找并安装驱动程序软件。

3. 在 TD 软件安装路径的 “driver” 目录下，根据自己计算机系统选择合适的驱动路径

[浏览计算机上的驱动程序文件](#)

在以下位置搜索驱动程序软件:

包括子文件夹(I)

4. 点击 “下一步”，看到 “Anlogic usb cable v0.1” 说明驱动安装成功。

[已安装适合设备的最佳驱动程序软件](#)

Windows 已确定该设备的驱动程序软件是最新的。

Anlogic usb cable v0.1

### 三、 开发板资源介绍

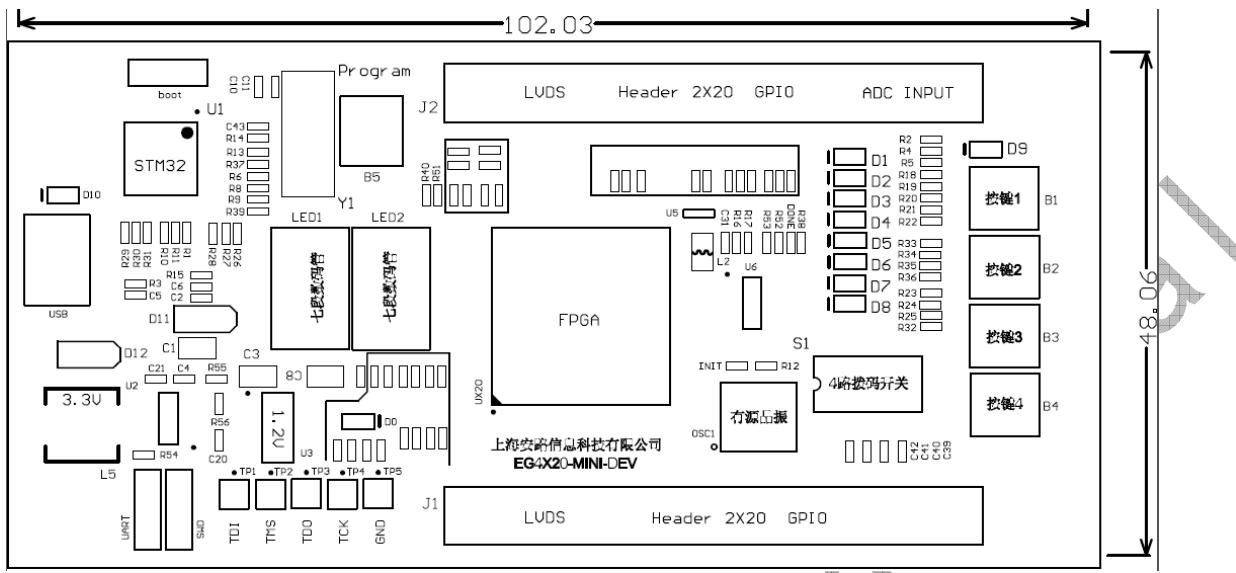

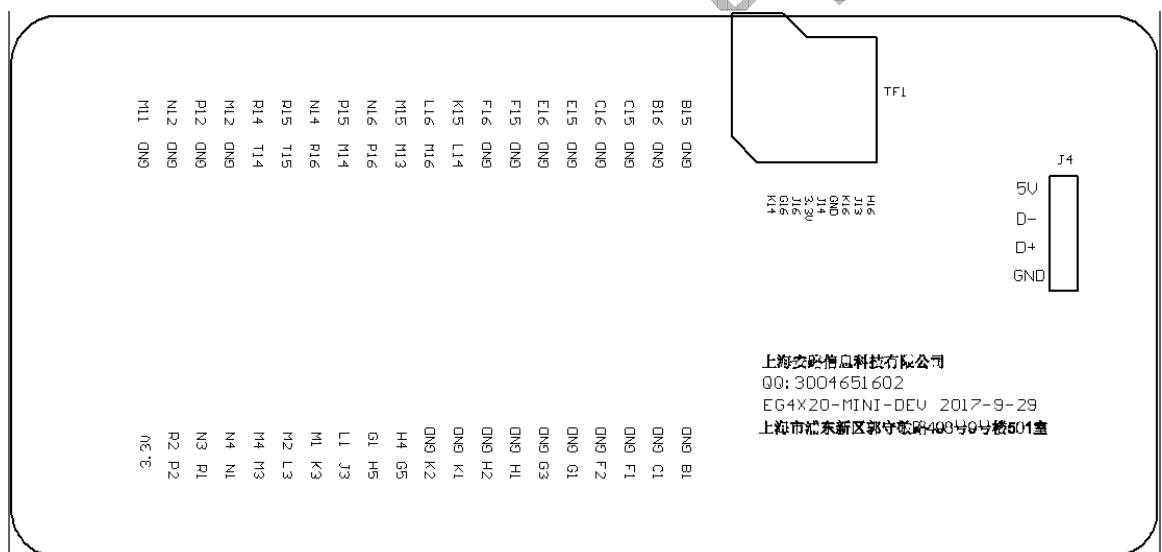

## 丝印顶层视图

## 丝印底层视图

开发板背面的排针、SD CARD 位置标注了部分 IO 管脚的位置。

## 1. 开发板指示灯

电路板中间的红色发光二极管 D0 为 3.3V 电源指示 ,指示灯亮表示开发板可以正常工作。 电路板左上角的绿色发光二极管 D10 为下载过程指示信号 ,FPGA 下载工程的过程中灯会闪烁 , 通过 USB 线接到电脑也会闪一下。

电路板右上角的绿色发光二极管 D9 为 FPGA 芯片 DONE 指示信号 , 常亮表示 FPGA 没有配置成功 ,FPGA 没有正常工作 ; FPGA 配置成功后灯会熄灭 ,FPGA 正在工作。 开发板刚上电的时候 D9 会亮 , 如果 FLASH 有正确位流 ,FPGA 自动从 FLASH 加载程序 , 成功以后 D9 熄灭。

## 2. 电源

开发板电源通过 USB 口 5V 供电 , 一般使用时计算机的 USB 口供电足够 , 若 FPGA 程序复杂 , 频率较高情况下 ,FPGA 工作电流可能会超过计算机 USB 最大供电能力 ( 500mA ) , 供电不足导致开发板工作不稳定 , 可以通过 USB 口后面的单排针 J4 提供外部 5V 供电 , 通过外部的 5V 电流不会流向 micro usb 口。

开发板的 3.3V 电压通过 APW7322 电源芯片转换而来 , 电感 L5 能通过的最大电流是 1.7A , 3.3V 电压为 FPGA 提供 IO bank 电压、 AUX 电压。

FPGA 核心电压 1.2V 由 3.3V 通过 LM1117-1.2 电源芯片转换而来 , 核心电流大小会因工程而异。

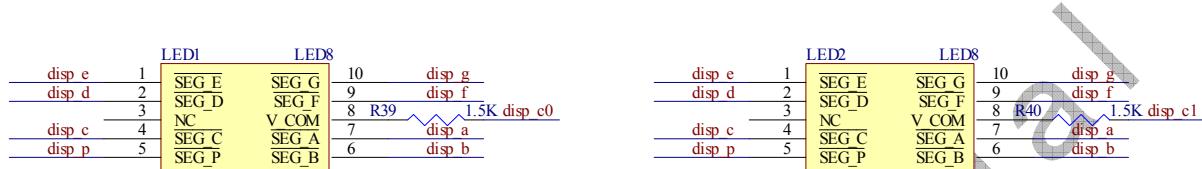

### 3. 数码管

开发板 FPGA 芯片左边有 2 个七段共阳动态带点数码管，段码低电平有效，位码高电平有效。数码管位码信号串来了 1.5K 的限流电阻，数码管工作电流在 2mA 左右。

**SEG**

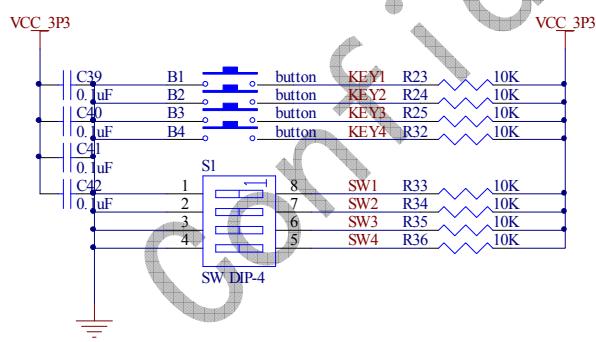

### 4. 按键、拨码开关

**KEY BUTTON**

按键跟拨码开关都有 10K 的上拉电阻，按键按下去是 “0”，按键释放是 “1”，

拨码开关拨上 ON 状态下是 “0”，拨到下面是 OFF 状态 “1”。

开发左上边有个 program 按键，可让 FPGA 在不断电的情况下从 FLASH 重新加载。

至于工程的全局复位 rst\_n 功能的按键，用户可从 B1~B4 的可编程按键中定义。

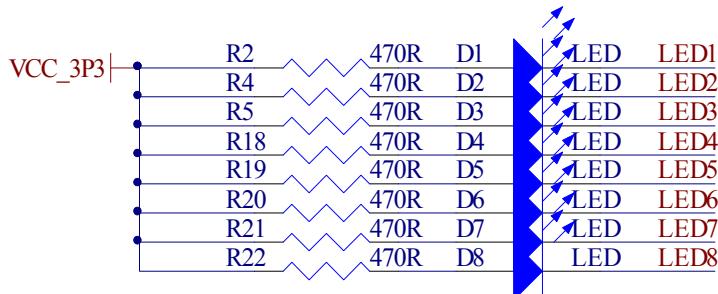

## 5. 8 路可编程 LED 指示灯

LED 灯低电平亮

## 6. GPOP 口

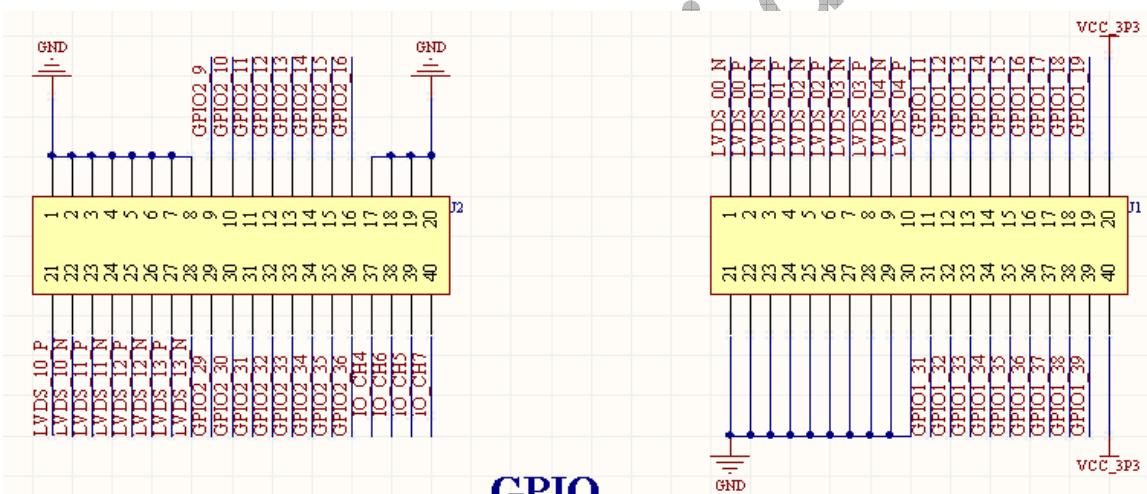

开发板上下各一排 2x20 的双排针 J1、J2。

J1 口包含了 5 对 LVDS 口，LVDS 口对面的排针均为 GND，最右边有 3.3V 输出。

J2 口包含了 4 对 LVDS 口，LVDS 口对面的排针均为 GND。J2 右边接了 4 个 ADC 采样通道，分别是通道 4/6/5/7, ADC 模块参考电压是 REF3012C 产生的 1.25V。ADC 模块的使用、注意事项参看参考工程。GPIO 口的其它管脚可以接其它外设，功能用户定义。

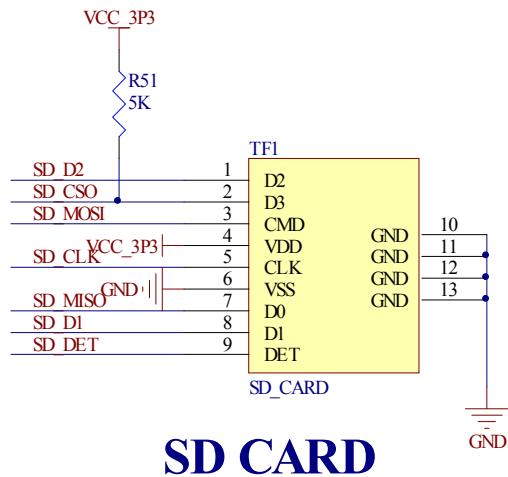

## 7. SD CARD 模块

SD 卡接了 7 个 IO 口到 FPGA，可以做 SD 卡全模式设计，考虑到 SD 卡座的尺寸以及板子空间，将卡座放到了板子背面，并且没有焊接。

## 8. 资源分配表

|                  |         | 网络标号  | 管脚名称 |

|------------------|---------|-------|------|

| 有源晶振             |         | GCLK1 | P1   |

| 拨<br>码<br>开<br>关 | SW1     | C4    |      |

|                  | SW2     | M7    |      |

|                  | SW3     | P7    |      |

|                  | SW4     | P6    |      |

|                  | KEY1    | A15   |      |

| 按<br>键           | KEY2    | B14   |      |

|                  | KEY3    | A14   |      |

|                  | KEY4    | B13   |      |

|                  | LED1    | T9    |      |

| L<br>E<br>D<br>灯 | LED2    | R9    |      |

|                  | LED3    | T8    |      |

|                  | LED4    | T7    |      |

|                  | LED5    | R7    |      |

|                  | LED6    | P8    |      |

|                  | LED7    | P9    |      |

|                  | LED8    | N9    |      |

|                  | disp_a  | A13   |      |

| 数<br>码<br>管      | disp_b  | A14   |      |

|                  | disp_c  | B6    |      |

|                  | disp_d  | A6    |      |

|                  | disp_e  | A7    |      |

|                  | disp_f  | B12   |      |

|                  | disp_g  | A12   |      |

|                  | disp_p  | A5    |      |

|                  | Disp_c0 | B14   |      |

| SD CARD          | Disp_c1 | C13   |      |

|                  | SD_CS0  | G16   |      |

|                  | SD_CLK  | J14   |      |

|                  | SD_D1   | J13   |      |

|                  | SD_D2   | K14   |      |

|                  | SD_MOSI | J16   |      |

|                  | SD_MISO | K16   |      |

|                  | SD_DET  | H16   |      |

| GPIO |           |      |           |

|------|-----------|------|-----------|

| J1   | 网络标号      | 管脚名称 | J2        |

|      | LVDS_00_P | C1   | LVDS_10_P |

|      | LVDS_00_N | B1   | LVDS_10_N |

|      | LVDS_01_P | F2   | LVDS_11_P |

|      | LVDS_01_N | F1   | LVDS_11_N |

|      | LVDS_02_P | G3   | LVDS_12_P |

|      | LVDS_02_N | G1   | LVDS_12_N |

|      | LVDS_03_P | H2   | LVDS_13_P |

|      | LVDS_03_N | H1   | LVDS_13_N |

|      | LVDS_04_P | K2   | GPIO2_9   |

|      | LVDS_04_N | K1   | GPIO2_10  |

|      | GPIO1_11  | G5   | GPIO2_11  |

|      | GPIO1_12  | H5   | GPIO2_12  |

|      | GPIO1_13  | J3   | GPIO2_13  |

|      | GPIO1_14  | K3   | GPIO2_14  |

|      | GPIO1_15  | L3   | GPIO2_15  |

|      | GPIO1_16  | M3   | GPIO2_16  |

|      | GPIO1_17  | N1   | GPIO2_29  |

|      | GPIO1_18  | R1   | GPIO2_30  |

|      | GPIO1_19  | P2   | GPIO2_31  |

|      | GPIO1_31  | H4   | GPIO2_32  |

|      | GPIO1_32  | J1   | GPIO2_33  |

|      | GPIO1_33  | L1   | GPIO2_34  |

|      | GPIO1_34  | M1   | GPIO2_35  |

|      | GPIO1_35  | M2   | GPIO2_36  |

|      | GPIO1_36  | M4   | IO_CH4    |

|      | GPIO1_37  | N4   | IO_CH6    |

|      | GPIO1_38  | N3   | IO_CH5    |

|      | GPIO1_39  | R2   | IO_CH7    |

## 结束语：

上海安路信息科技有限公司提供的 EG4X20-MINI-DEV 开发板所有的资源介绍均有相关的参考工程，希望我们的 FPGA 芯片、我们的支持能给大家评估提供方便，网盘链接提供了 FPGA 开发软件、原理图资料、参考工程。TD 软件会定期提供更新。

百度网盘链接：<http://pan.baidu.com/s/1bzNTro>    密码：a7w9

祝大家工作学习愉快。

安路支持 QQ：3004651602

2017-10-16

勘误：

Analogic Confidential