# 16+1 ports Ethernet Switch Controller with Octal-PHYs (Priority, Security & Protocol)

#### **Features**

- Built in 8 internal PHY, 8 SS-SMII, and one MII

- 1.25Mbits packet buffer memory

- Support packet length up to 1600 Bytes

- Store & forward, share memory, non-blocking architecture

- Support flow control

- 802.3x in full duplex

- Collision / Carrier sense based backpressure in half duplex

- Provide up to 4K MAC address entries

- CRC/ direct hashing algorithm

- Programmable aging timer (55s~1812070.4s)

- Wire speed address learning and resolution

- CPU accessible for security and static MAC

- Learning enable/disable

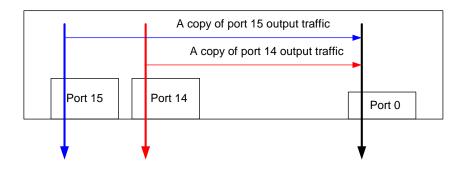

- Support Sniffer function (in, out, in & out)

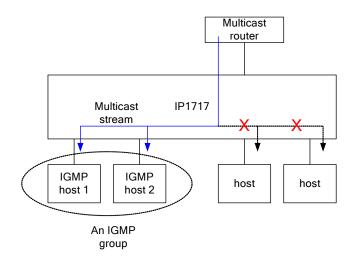

- Support IGMP snooping function Version 1,2

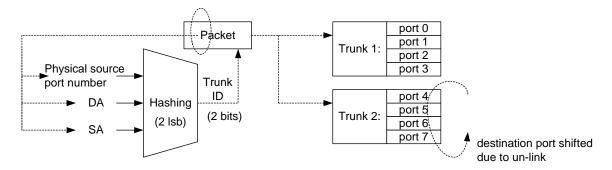

- Support up to 2 trunk group

- Support up to 2 trunk groups

- (Port 0~3, port 4~7)

- Load balance based on (port, DA, SA, DA / SA)

- Support VLAN(20 VLAN groups)

- Port based VLAN

- Tag based VLAN based on Ports & VIDs

- Add/ remove/ modify tag

- Support Class of Service

- Port based COS function

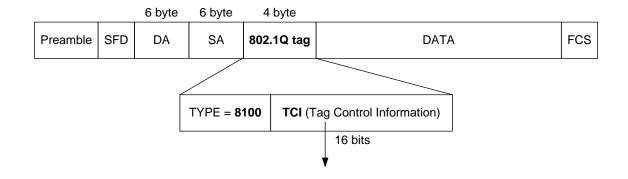

- 802.1Q priority tag based

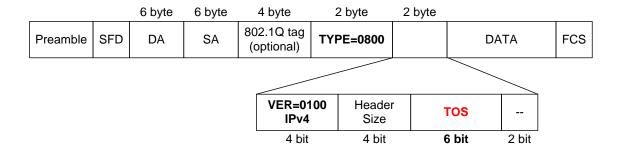

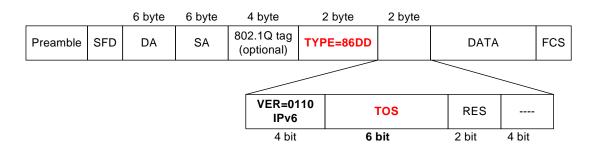

- IP TOS based (IPv4/IPv6)

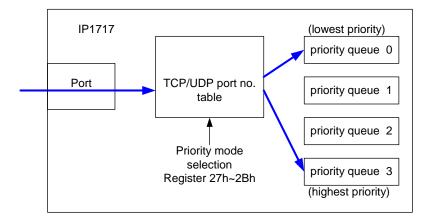

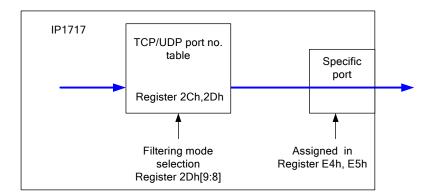

- TCP/UDP port based

- 4 queues for per port

- WRR/ FIFS/ SP algorithm

- Broadcast storm control support

- Broadcast rate control per port

- Block broadcast packet that not belongs to ARP or IPv4 packet to CPU port

- Support port security

- MAC address based

- TCP/UDP port based

- **Supports Bandwidth control** 255 configurable levels for P0-P16, (from 32kbps to 7.96 Mbps) for low bandwidth

- 255 configurable levels for P0-P16 (from 512kbps to 100 Mbps) for high bandwidth

- With/without flow control

- Support SMI auto-polling function

- Poll for speed, duplex, flow control, and link

- Support Reverse MII 100M full duplex only

- CPU accessible (interrupt support)

- CPU R/W PHY registers

- Support SS-SMII mode

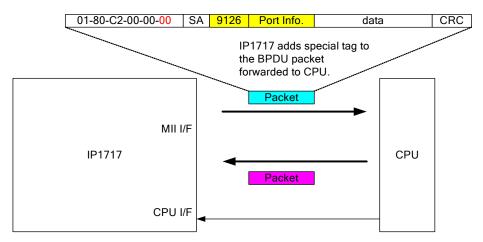

- Support 4 port states for Spanning Tree protocol

- Discarding/Blocking/learning/ forwarding

- Forward BPDU to CPU port

- Captures specific packet to CPU port

- BPDU, LACP, 802.1X, GMRP, GVRP, ARP

- ICMP, IGMP, TCP, UDP, OSPF, other IP protocols

- Packets with specific TCP/UDP port number

- Flexible PHY address setting for CPU.

- Support three Configuration modes

- Pin initial setting

- 2 wire serial interface for EEPROM

- 2 wire serial interface for CPU

- Statistic counters for each port

- RX/TX packet count

- CRC error packet count

- Drop packet count

- Collision count

- Support Non association port

- Support port based address flush

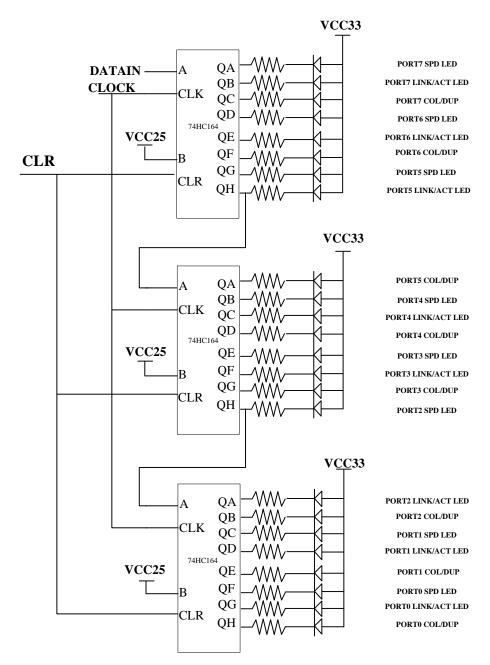

- Support LED functions (for p0~p7)

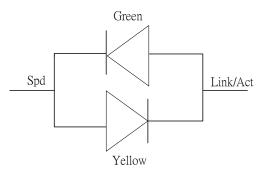

- Support 2 bit serial, 3 bit serial, and 3 bit bi color mode

- Support direct LED mode for Link/Activity, speed, duplex states

- Support bi color direct LED mode

- Only one 25MHz crystal is needed

- Adjustable IO voltage (3.3v MII1.95V SS-SMII)

- Programmable MAC address table through CPU interface

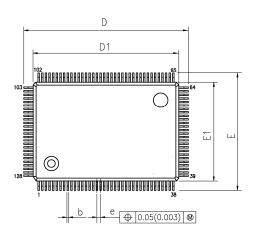

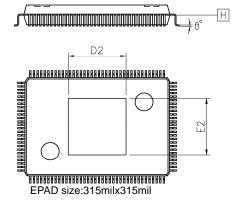

#### 128 pin LQFP EPAD package

## **General Description**

The IP1717 is a cost effective and fully integrated single chip. It integrates a 17-port switch controller, an octal PHY transceiver and SSRAM. Each of PHY transceiver complies with 802.3u specification and HP-license Auto MDI/MDIX.

The IP1717 also provides a 3S-MII interface to connect an octal PHY for a 16-port dumb switch application and a MII interface for a smart/management switch application.

It supports full smart switch functions, including IGMP snooping, 4 priority queues, TOS, TCP/UDP port number priority, 802.1Q VLAN, port security, protocol filter/forwarding and bandwidth control.

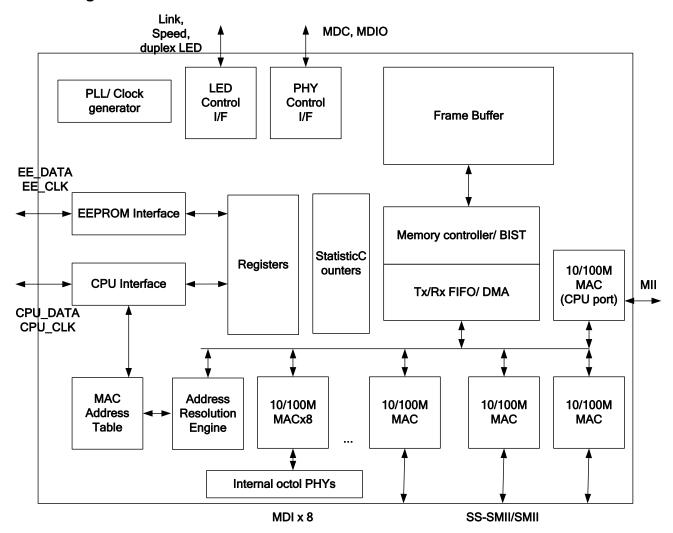

## **Block diagram**

# **Table of Contents**

| Features        | 1                                        | 1        |

|-----------------|------------------------------------------|----------|

| General Desc    | ription                                  | 2        |

| Block diagran   | )3                                       | 3        |

| Table of Cont   | ents4                                    | ļ        |

| Revision Hist   | ory6                                     | 3        |

| Disclaimer      |                                          | ;        |

| Application D   | agram 7                                  | 7        |

| Pin diagram.    | 8                                        | 3        |

|                 | iption9                                  |          |

| Pin description | n (continue)                             | )        |

|                 | n (continue)11                           |          |

| Pin description | n (continue) latch in pins13             | 3        |

| Pin description | n (continue) latch in pins15             | 5        |

| 2 Function      | description                              | 3        |

| 2.1             | witch engine and queue management16      | ;        |

| 2.1.            | Address learning and hashing16           | ;        |

| 2.1.2           | 802.1D packet forward16                  | ;        |

| 2.1.3           | Inter frame gap compensation16           | ;        |

| 2.2 A           | ging time 17                             | 7        |

| 2.2.            |                                          | 7        |

| 2.2.2           |                                          |          |

|                 | low control17                            |          |

| 2.3.            |                                          |          |

| 2.3.2           | =                                        |          |

|                 | andwidth and broadcast storm control18   |          |

| 2.4.            |                                          |          |

| 2.4.2           |                                          |          |

| 2.4.3           |                                          |          |

|                 | S-SMII and MII interface19               |          |

| 2.5.            | <b>5</b>                                 |          |

| 2.5.2           | <b>3</b>                                 |          |

|                 | PU interface                             |          |

|                 | onfigure and access the port status      |          |

|                 | III port force link                      |          |

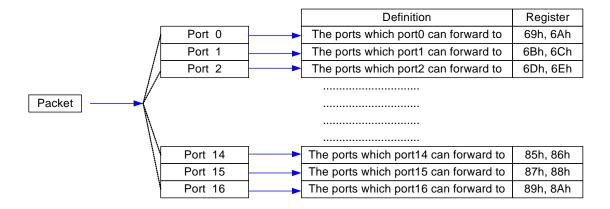

| 2.9 F           | ead /Write address table(LUT)            | 1        |

| 2.10            | PU read /write PHY registers             | <u>'</u> |

|                 | PU read/write EEPROM                     |          |

| _               | EPROM interface 22 tatistics counters 23 |          |

|                 |                                          | -        |

|                 | terrupt                                  |          |

|                 | ED description                           |          |

| 2.15            | <b>U</b>                                 |          |

| 2.15            | 3 3                                      |          |

| 2.15            | ·                                        |          |

| 2.15<br>2.15    |                                          |          |

| 2.15            | · ·                                      |          |

|                 | 6 Advanced power saving mode             |          |

| 2.16 V<br>2.16  |                                          |          |

| 2.16            |                                          |          |

| 2.16            | <b>5</b>                                 |          |

| 2.10            | Add/Nethove/Modify rag28                 | ,        |

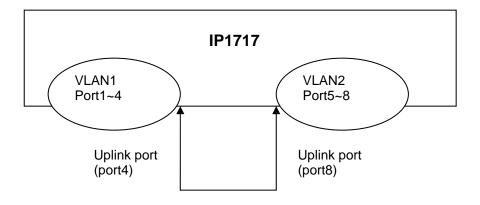

|   | 2.16.4                        | Packet across a VLAN                           | . 30 |

|---|-------------------------------|------------------------------------------------|------|

|   | 2.16.5                        | VLAN up link                                   | . 30 |

|   | 2.17 Class of serv            | ice                                            |      |

|   | 2.17.1                        | Output queue with scheduling priority          | . 31 |

|   | 2.17.2                        | Port base COS                                  |      |

|   | 2.17.3                        | 802.1Q priority tag based COS                  | . 32 |

|   | 2.17.4                        | IP TOS based COS                               |      |

|   | 2.17.5                        | TCP/UDP port number based COS                  | . 33 |

|   | 2.18 Capture Ethe             | ernet protocol frame and IP packet to CPU port |      |

|   | 2.18.1                        | In band management frame                       |      |

|   | 2.18.2                        | ARP 802.1X                                     |      |

|   | 2.18.3                        | BPDU, LACP, GVRP, GMRP                         | . 36 |

|   | 2.18.4                        | ICMP TCP, UDP, OSPF                            | . 37 |

|   | 2.18.5                        | The other IPV4                                 |      |

|   | 2.18.6                        | Block broadcast packet to CPU                  |      |

|   | 2.19 Security                 |                                                |      |

|   | 2.19.1                        | MAC address based security                     | . 37 |

|   | 2.19.2                        | 802.1X port based security                     |      |

|   | 2.19.3                        | Specific port filtering                        |      |

|   | 2.19.4                        | Port mirror security                           |      |

|   | 2.20 Trunk channe             | el                                             | . 39 |

|   | 2.20.1                        | Trunk channel behavior                         | . 39 |

|   | 2.20.2                        | Load balance                                   | . 40 |

|   | 2.21 Spanning tree            | e function                                     | . 41 |

|   | 2.21.1                        | BPDU packet forwarding                         |      |

|   | 2.21.2                        | Spanning tree setting                          | . 41 |

|   | 2.22 Non associat             | ion port                                       |      |

|   | 2.23 Aging flush              |                                                | . 42 |

|   | 2.24 IGMP snoopi              | ng                                             | . 42 |

|   | 2.25 Special tag              | -                                              | . 43 |

| 3 |                               |                                                |      |

|   | 3.1 IP1717 switch             | h register description                         | . 44 |

|   | 3.2 IP1717 intern             | nal octal PHY register description             | . 63 |

| 4 | <b>Electrical Characteris</b> | stics                                          | . 67 |

|   | 4.1 Absolute Max              | ximum Rating                                   | . 67 |

|   | 4.2 AC Characte               | ristics                                        | . 68 |

|   | 4.3 DC Characte               | ristics                                        | . 74 |

| 5 | Order Information             |                                                | . 75 |

| 6 | Package Detail                |                                                | 76   |

# **Revision History**

| IP1717-DS-R01   Initial Release     IP1717-DS-R02   1.Modify COL LED blinking function in LEDMODE[1:0]=10 (page14 and 23)     2.Remove SMII, Only SS-SMII is supported by IP1717     3.Modify pin description of pin 99 BLK_TIME     4.HOME_VLAN_OFF pin setting changed to pin 97     5.Modify BPDU description, refer to General MAC operation behavior register(page 40)     6.Fix incorrect pin diagram(page 7)     1.P1717-DS-R03   1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)     1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23)     2. Support advanced power saving mode(page 26)     3.Add priority field of VLAN tag mapping to output queue description(page 30)     4.Add WRR ratio description of queue(page 30&50)     5.Fix MDC/MDIO timing(page 6)     6.Fix incorrect register definition for backpressure(page 16)     9.Add DC characteristics description for VDDIO_1(page74)     10.Add the description of the TCP/UDP port number and the user-defined port number.(page 32)     11.Modify the description of the TCP/UDP port number and the user-defined port number.(page 32)     13.Modify the description of the TCP/UDP port number and the user-defined port number.(page 32)     14.Add DC characteristics description for cystal(X1)(page 74)     15.Add AC characteristics description for cystal(X1)(page 74)     16.Modify the description of the TOP Nabage COO(page 46)     19. Add MC address description for or switch(page 18)     19. Add MC address description for Deventage 29     17. Add TX pause description for absolute maximum rating(page 68)     21. Add the description of the splithy port(page 29)     17. Add TX pause description for description(page 48)     20.Modify the description of the Splithy port (page 48)     20.Modify the description of the Splithy port (page 48)     21. Add the description of the splithy port (page 68)     22. Add RESETB threshold voltage description(page 74)     23. Add RESETB threshold voltage description(pa   | Revision #    | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

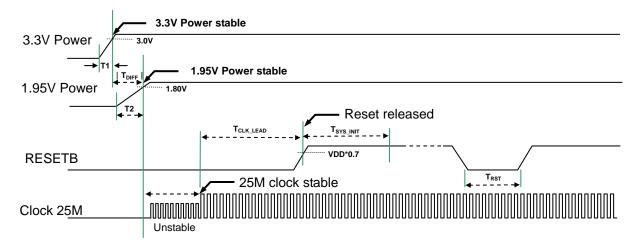

| 2.Remove SMII, Only SS-SMII is supported by IP1717  3.Modify pin description of pin 99 BLK_TIME  4.HOME_VLAN_OFF pin setting changed to pin 97  5.Modify BPDU description, refer to General MAC operation behavior register(page 40)  6.Fix incorrect pin diagram(page 7)  1.Pix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  1.Pix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  1.Add interrupt events respond time description of CPU R/W EEPROM, SMII, and PHY link stat change(page 23)  2.Support advanced power saving mode(page 26)  3.Add priority field of VLAN tag mapping to output queue description(page 30)  4. Add VRR ratio description of queue(page 30850)  5.Fix MDC/MDIO timing( page 6)  6.Fix incorrect MII transmit and receive timing (page 69)  7.Add special tag description(page 42)  8.Fix incorrect register definition for backpressure(page 16)  9.Add DC characteristics description for VDDIO_1(page74)  10. Add the description of the TCP/UDP port number and the user-defined port number.(page 32)  11.Modify the description of the TCP/UDP port number and the user-defined port number.(page 32)  13.Modify the description of the TCP/UDP port number and the user-defined port number. (page 32)  14.Add DC characteristics description for crystal(X1)(page 74)  15.Add AC characteristics description for crystal(X1)(page 74)  15.Add AC characteristics description for power sequence(page 65)  16.Modify the description of the uplink port(page 18)  19.Add MAC address description for switch(page 16)  19.Add MAC address description for Devoluge 48)  20.Modify the description of absolute maximum rating(page 68)  21.Add the description of the Spd/Duplex LEDs in force mode(page 24,62)  22.Modify the setting of register 02h[5] to be reserved(page 43)  23.Fix the error of 3-bit Bi-color LED setting(page 26)  24.Add junction temperature description (page 74)  26.Add the register description of the internal octal PHY(page64-66)  27.Add Crystal specification descriptio | IP1717-DS-R01 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.Modify pin description of pin 99 BLK_TIME 4.HOME_VLAN_OFF pin setting changed to pin 97 5.Modify BPDU description, refer to General MAC operation behavior register(page 40) 6.Fix incorrect pin diagram(page 7)  IP1717-DS-R03 1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23) 2.Support advanced power saving mode(page 26) 3.Add priority field of VLAN tag mapping to output queue description(page 30) 4.Add WRR ratio description of queue(page 30&50) 5.Fix MDC/MDIO timing( page 6) 6.Fix incorrect MII transmit and receive timing (page 69) 7.Add special tag description(page 42) 8.Fix incorrect register definition for backpressure(page 16) 9.Add Dc characteristics description for VDIIO_1(page74) 10.Add the description of the TCP/UDP port number and the user-defined port number.(page 32) 11.Modify the description of the Switch ID(page 20) 13.Modify the description of IP TOS based COS(page 32) 14.Add Dc Characteristics description for crystal(X1)(page 74) 15.Add AC characteristics description for crystal(X1)(page 74) 15.Add AC characteristics description for power sequence(page 65) 16.Modify the description of the uplink port(page 16) 18.Modify port number usage description for protocol(page 46) 19.Add MAC address description for switch(page 16) 19.Add MAC address description for switch(page 16) 19.Add MAC address description for protocol(page 46) 19.Add MAC address description for be be reserved(page 43) 23.Fix the error of 3-bit Bi-color LED setting(page 26) 24.Add junction temperature description(page 76) 28.Modify Power On Sequence and Reset Timing(page 68) 25.Add RESETB threshold voltage description(page 73) 28.Modify Power On Sequence and Reset Timing(page 68) 29.Remove IP security function description(page 73) 30.Modify VLAN group description(page 73) 31.Add EEPROM timing specification(page 73) 32.Modify MDC/MDIO and CPUCLK/CPUDATA timing specification(page 70,71)        | IP1717-DS-R02 | 1.Modify COL LED blinking function in LEDMODE[1:0]=10 (page14 and 23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.HOME_VLAN_OFF pin setting changed to pin 97  5.Modify BPDU description, refer to General MAC operation behavior register(page 40) 6.Fix incorrect pin diagram(page 7)  1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23) 2.Support advanced power saving mode(page 26) 3.Add priority field of VLAN tag mapping to output queue description(page 30) 4.Add WRR ratio description of queue(page 308.50) 5.Fix MDC/MDIO timing (page 6) 6.Fix incorrect MII transmit and receive timing (page 69) 7.Add special tag description(page 42) 8.Fix incorrect register definition for backpressure(page 16) 9.Add DC characteristics description for VDDIO_1 (page74) 10.Add the description of the TCP/UDP port number and the user-defined port number.(page 32) 11.Modify the description of the Switch ID(page 20) 13.Modify the description of the Switch ID(page 20) 13.Modify the description of IP TOS based COS(page 32) 14.Add DC characteristics description for crystal(K1)(page 74) 15.Add AC characteristics description for protocol(page 46) 18.Modify port number usage description for protocol(page 46) 19.Add MAC address description for PUP(page 48) 20.Modify the description of the Spid-Duplex LEDs in force mode(page 24,62) 22.Modify the setting of register 02/hS to be reserved(page 43) 23.Fix the error of 3-bit Bi-color LED setting(page 26) 24.Ad junction temperature description(page 76) 25.Add RESETB threshold voltage description(page 78) 26.Add the register description of the internal octal PHY(page64~66) 27.Add Crystal specification description(page 73) 28.Modify Power On Sequence and Reset Timing(page 38) 29.Remove IP security function description(page 73) 31.Add EEPROM timing specification(page 73) 32.Modify MC/MDIO and CPUCLK/CPUDATA timing specification(page 70,71)                                                                                                                                           |               | 2.Remove SMII, Only SS-SMII is supported by IP1717                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.HOME_VLAN_OFF pin setting changed to pin 97  5.Modify BPDU description, refer to General MAC operation behavior register(page 40) 6.Fix incorrect pin diagram(page 7)  1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23) 2.Support advanced power saving mode(page 26) 3.Add priority field of VLAN tag mapping to output queue description(page 30) 4.Add WRR ratio description of queue(page 308.50) 5.Fix MDC/MDIO timing (page 6) 6.Fix incorrect MII transmit and receive timing (page 69) 7.Add special tag description(page 42) 8.Fix incorrect register definition for backpressure(page 16) 9.Add DC characteristics description for VDDIO_1 (page74) 10.Add the description of the TCP/UDP port number and the user-defined port number.(page 32) 11.Modify the description of the Switch ID(page 20) 13.Modify the description of the Switch ID(page 20) 13.Modify the description of IP TOS based COS(page 32) 14.Add DC characteristics description for crystal(K1)(page 74) 15.Add AC characteristics description for protocol(page 46) 18.Modify port number usage description for protocol(page 46) 19.Add MAC address description for PUP(page 48) 20.Modify the description of the Spid-Duplex LEDs in force mode(page 24,62) 22.Modify the setting of register 02/hS to be reserved(page 43) 23.Fix the error of 3-bit Bi-color LED setting(page 26) 24.Ad junction temperature description(page 76) 25.Add RESETB threshold voltage description(page 78) 26.Add the register description of the internal octal PHY(page64~66) 27.Add Crystal specification description(page 73) 28.Modify Power On Sequence and Reset Timing(page 38) 29.Remove IP security function description(page 73) 31.Add EEPROM timing specification(page 73) 32.Modify MC/MDIO and CPUCLK/CPUDATA timing specification(page 70,71)                                                                                                                                           |               | 3.Modify pin description of pin 99 BLK_TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.Fix incorrect pin diagram(page 7)  IP1717-DS-R03  1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)  IP1717-DS-R04  1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23)  2.Support advanced power saving mode(page 26)  3.Add priority field of VLAN tag mapping to output queue description(page 30)  4.Add WRR ratio description of queue(page 30850)  5.Fix MDC/MDIO timing( page 6)  6.Fix incorrect MII transmit and receive timing (page 69)  7.Add special tag description(page 42)  8.Fix incorrect register definition for backpressure(page 16)  9.Add DC characteristics description for VDDIO_1(page74)  10.Add the description of the TCP/UDP port number and the user-defined port number.(page 32)  11.Modify the description of the Switch ID(page 20)  13.Modify the description of IP TOS based COS(page 32)  14.Add DC characteristics description for crystal(X1)(page 74)  15.Add AC characteristics description for crystal(X1)(page 74)  15.Add AC characteristics description for protocol(page 46)  16.Modify the description of the uplink port(page 29)  17.Add TX pause description for switch(page 16)  18.Modify but description for switch(page 16)  19.Add MAC address description for CPU(page 48)  20.Modify the description for absolute maximum rating(page 68)  21.Add the description of the Spd/Duplex LEDs in force mode(page 24,62)  22.Modify the setting of register 02h[5] to be reserved(page 43)  23.Fix the error of 3-bit Bi-color LED setting(page 26)  24.Add junction temperature description(page 76)  28.Modify Power On Sequence and Reset Timing(page 68)  29.Remove IP security function description(page 75)  28.Modify Power On Sequence and Reset Timing(page 68)  29.Remove IP security function description(page 73)  31.Add EEPROM timing specification(page 73)  31.Add EEPROM timing specification(page 73)  31.Add EEPROM timing specification(page 70,71)                                                                                                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IP1717-DS-R04  1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link stat change(page 23) 2. Support advanced power saving mode(page 26) 3.Add priority field of VLAN tag mapping to output queue description(page 30) 4. Add WRR ratio description of queue(page 30&50) 5. Fix MDC/MDIO timing( page 6) 6. Fix incorrect MII transmit and receive timing (page 69) 7. Add special tag description(page 42) 8. Fix incorrect register definition for backpressure(page 16) 9. Add DC characteristics description for VDDIO_1(page74) 10. Add the description of the TCP/UDP port number and the user-defined port number.(page 32) 11. Modify the description of the memory buffer size(page 1) 12. Add the description of the Switch ID(page 20) 13. Modify the description for IP TOS based COS(page 32) 14. Add DC characteristics description for rystal(X1)(page 74) 15. Add AC characteristics description for power sequence(page 65) 16. Modify the description of the uplink port(page 29) 17. Add TX pause description for witch(page 16) 18. Modify port number usage description for protocol(page 46) 19. Add MAC address description for CPU(page 48) 20. Modify the description for switch(page 16) 18. Modify port number usage description for protocol(page 46) 19. Add MAC address description for CPU(page 48) 20. Modify the description for about the maximum rating(page 68) 21. Add the description of the Spd/Duplex LEDs in force mode(page 24,62) 22. Modify the description for about the maximum rating(page 68) 25. Add RESETB threshold voltage description(page 74) 26. Add the register description (page 75) 28. Modify Power On Sequence and Reset Timing(page 68) 29. Remove IP security function description(page 73) 30. Modify MDC/MDIO and CPUCLK/CPUDATA timing specification(page 70,71)                                                                                                                                                                                                                                                              |               | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| change(page 23)  2. Support advanced power saving mode(page 26)  3. Add priority field of VLAN tag mapping to output queue description(page 30)  4. Add WRR ratio description of queue(page 30&50)  5. Fix MDC/MDIO timing( page 6)  6. Fix incorrect MII transmit and receive timing (page 69)  7. Add special tag description(page 42)  8. Fix incorrect register definition for backpressure(page 16)  9. Add DC characteristics description for VDDIO_1(page74)  10. Add the description of the TCP/UDP port number and the user-defined port number.(page 32)  11. Modify the description of the TWP/UDP port number and the user-defined port number. (page 32)  12. Add the description of the Switch ID(page 20)  13. Modify the description of IP TOS based COS(page 32)  14. Add DC characteristics description for crystal(X1)(page 74)  15. Add AC characteristics description for crystal(X1)(page 74)  15. Add AC characteristics description for power sequence(page 65)  16. Modify the description of the uplink port(page 29)  17. Add TX pause description for switch(page 16)  18. Modify port number usage description for protocol(page 46)  19. Add MAC address description for CPU(page 48)  20. Modify the description for Abouter maximum rating(page 68)  21. Add the description of the Spd/Duplex LEDs in force mode(page 24,62)  22. Modify the description for LD setting(page 26)  24. Add junction temperature description(page 74)  26. Add the register description of the internal octal PHY(page64–66)  27. Add Crystal specification description(page 75)  28. Modify Power On Sequence and Reset Timing(page 68)  29. Remove IP security function description(page 73)  30. Modify VLAN group description(page 73)  32. Modify MDC/MDIO and CPUCLK/CPUDDATA timing specification(page 70,71)                                                                                                                                                                                                                                                                                            | IP1717-DS-R03 | 1.Fix P16 force link function description, refer to P16_FORCE_OFF pin description(Page11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

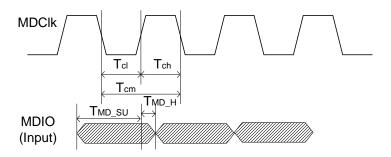

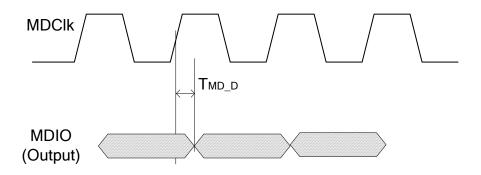

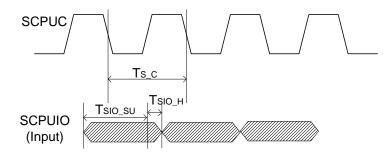

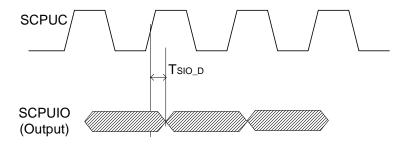

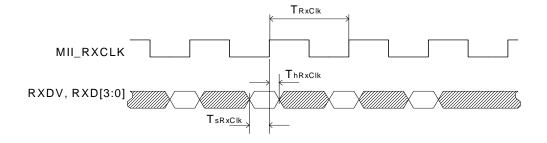

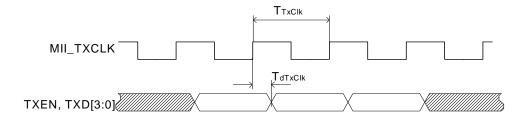

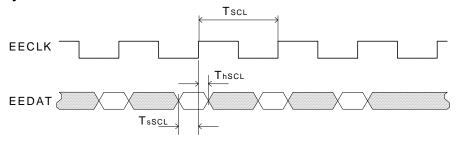

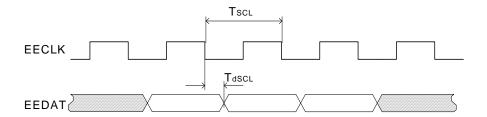

| 33. Modify Power On Sequence and Reset Himingroade 66)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | 1.Add interrupt events respond time description of CPU R/W EEPROM, SMI, and PHY link status change(page 23) 2. Support advanced power saving mode(page 26) 3. Add priority field of VLAN tag mapping to output queue description(page 30) 4. Add WRR ratio description of queue(page 30&50) 5. Fix MDC/MDIO timing(page 6) 6. Fix incorrect MII transmit and receive timing (page 69) 7. Add special tag description(page 42) 8. Fix incorrect register definition for backpressure(page 16) 9. Add DC characteristics description for VDDIO_1 (page74) 10. Add the description of the TCP/UDP port number and the user-defined port number.(page 32) 11. Modify the description of the TCP/UDP port number and the user-defined port number.(page 32) 13. Modify the description of the Switch ID(page 20) 13. Modify the description of TP TOS based COS(page 32) 14. Add DC characteristics description for crystal(X1)(page 74) 15. Add AC characteristics description for power sequence(page 65) 16. Modify the description of the uplink port(page 29) 17. Add TX pause description for switch(page 16) 18. Modify port number usage description for protocol(page 46) 19. Add MAC address description for cPU(page 48) 20. Modify the description of the Spd/Duplex LEDs in force mode(page 24,62) 22. Modify the setting of register 02h[5] to be reserved(page 43) 23. Fix the error of 3-bit Bi-color LED setting(page 26) 24. Add junction temperature description(page 68) 25. Add RESETB threshold voltage description(page 74) 26. Add the register description of the internal octal PHY(page64–66) 27. Add Crystal specification description(page 75) 28. Modify Power On Sequence and Reset Timing(page 68) 29. Remove IP security function description(page 73) 31. Add EEPROM timing specification(page 73) 32. Modify MDC/MDIO and CPUCLK/CPUDATA timing specification(page 70,71) |

| IP1717-DS-R05  1. Package changed to LQFP EPAD(page2,75,76)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IP1717-DS-R05 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **Disclaimer**

This document probably contains the inaccurate data or typographic error. In order to keep this document correct, IC Plus reserves the right to change or improve the content of this document.

# **Application Diagram**

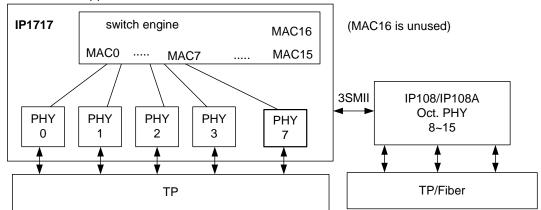

#### Dumb switch application

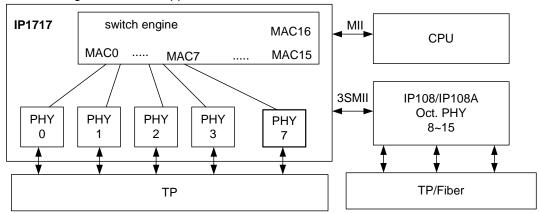

#### Smart/Management switch application

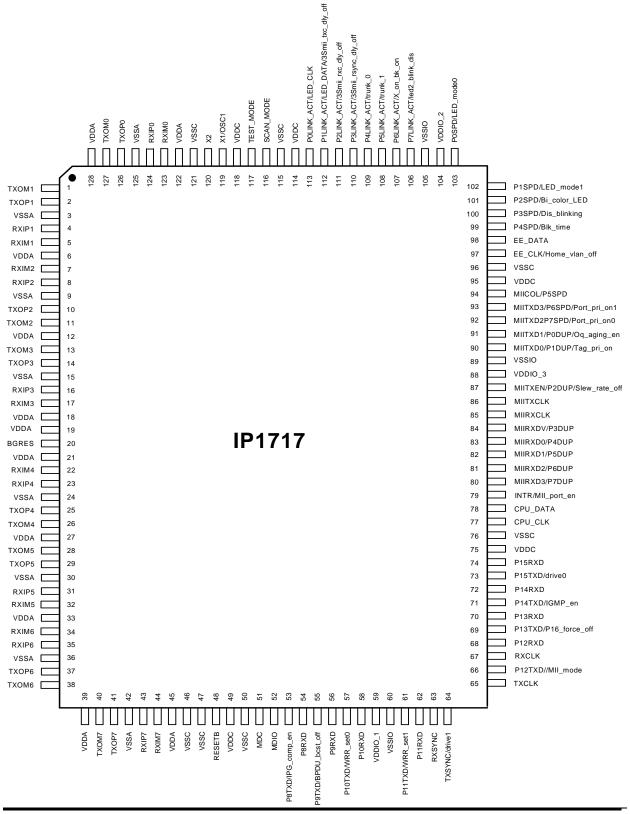

## Pin diagram

# 1 Pin description

| Pin No.                    | Label                                                                     | Туре | Description                                                                                                                  |  |

|----------------------------|---------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------|--|

| SS-SMII                    |                                                                           |      |                                                                                                                              |  |

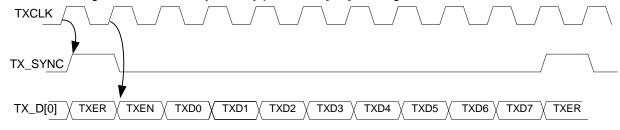

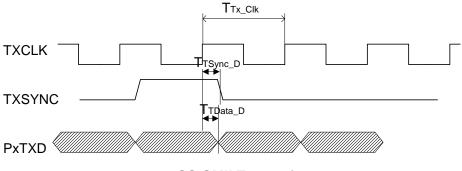

| 73,71,69,66<br>61,57,55,53 | P15TXD,<br>P14TXD, P13TXD,<br>P12TXD, P11TXD,<br>P10TXD, P9TXD,<br>P8TXD  | 0    | SS-SMII transmit data output for port 8 to port 15                                                                           |  |

| 64                         | TXSYNC                                                                    | 0    | SS-SMII synchronization output for transmit data                                                                             |  |

| 65                         | TXCLK                                                                     | 0    | SS-SMII transmit clock output                                                                                                |  |

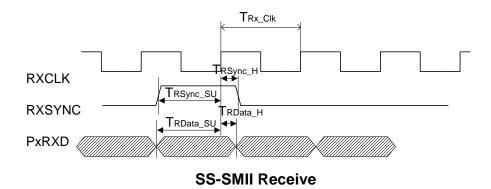

| 74,72,70,68<br>62,58,56,54 | P15RXD,<br>P14RXD, P13RXD,<br>P12RXD, P11RXD,<br>P10RXD, P9RXD,<br>P8RXD, | I    | SS-SMII receive data input for port 8 to port 15                                                                             |  |

| 63                         | RXSYNC                                                                    | I    | SS-SMII receive synchronization input                                                                                        |  |

| 67                         | RXCLK                                                                     | I    | SS-SMII receive clock input                                                                                                  |  |

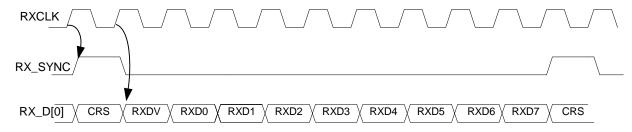

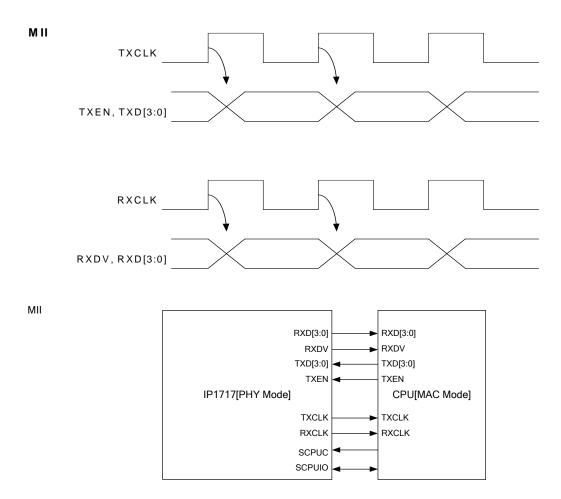

| MII/Reverse MII            | I                                                                         |      |                                                                                                                              |  |

| 87                         | MIITXEN                                                                   | 0    | MII (port 16) transmit enable                                                                                                |  |

| 94                         | MIICOL                                                                    | I/O  | MII (port 16) collision is an input driven by PHY in PHY mode. When in reverse MII mode, it is a output pin driven by IP1717 |  |

| 93,92,91,90                | MIITXD3~MIITXD0                                                           | 0    | MII (port 16) transmit data output                                                                                           |  |

| 84                         | MIIRXDV                                                                   | I    | MII (port 16) receive valid                                                                                                  |  |

| 80,81,82,83                | MIIRXD3~ MIIRXD0                                                          | I    | MII (port 16) receive data input                                                                                             |  |

| 86                         | MIITXCLK                                                                  | I/O  | O MII (port 16) transmit clock. Input for normal (MAC mod MII. Output for reverse (PHY mode) MII.                            |  |

| 85                         | MIIRXCLK                                                                  | I/O  | MII (port 16) receive clock. Input for normal (MAC mode) MII. Output for reverse (PHY mode) MII.                             |  |

| SMI                        |                                                                           |      |                                                                                                                              |  |

| 51                         | MDC                                                                       | 0    | Clock for serial management bus.                                                                                             |  |

|                            |                                                                           |      | It's recommended to add a 30pf capacitor to ground for noise filtering.                                                      |  |

| 52                         | MDIO                                                                      | I/O  | I/O data for serial management bus.                                                                                          |  |

|                            |                                                                           |      | It's recommended to add a 4.7K pull up resistor connecting to VDDIO_1 and a 30pf capacitor connecting to ground.             |  |

# Pin description (continue)

| Pin No.                       | Label                     | Type   | Description                                                                                                                                                         |

|-------------------------------|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEPROM                        |                           | 71     | ·                                                                                                                                                                   |

| 97                            | EE_CLK                    | 0      | Serial EEPROM clock output                                                                                                                                          |

| 98                            | EE_DATA                   | I/O    | Serial EEPROM data                                                                                                                                                  |

| PHY interface(A               | Auto-MDI/MDIX, HP-Lie     | cense) |                                                                                                                                                                     |

| 40,38,28,26,<br>13,11,1,127   | TXOM[7:0]                 | I/O    | Transmit/Receive output/input differential negative signal                                                                                                          |

| 41,37,29,25,<br>14,10,2,126   | TXOP[7:0]                 | I/O    | Transmit/Receive output/input differential positive signal                                                                                                          |

| 44,34,32,22,<br>17,7,5,123    | RXIM[7:0]                 | I/O    | Receive/Transmit input/output differential negative signal                                                                                                          |

| 43,35,31,23,<br>16,8,4,124    | RXIP[7:0]                 | I/O    | Receive/Transmit input/output differential positive signal                                                                                                          |

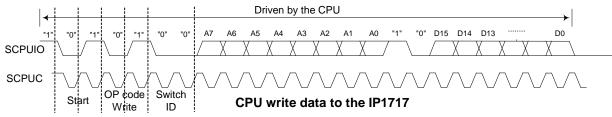

| CPU                           |                           |        |                                                                                                                                                                     |

| 77                            | CPU_CLK                   | I      | Serial CPU access clock input                                                                                                                                       |

| 78                            | CPU_DATA                  | I/O    | Serial CPU data                                                                                                                                                     |

| Serial LED                    |                           |        | ,                                                                                                                                                                   |

| 113                           | LED_CLK                   | 0      | Serial LED CLK                                                                                                                                                      |

| 112                           | LED_DATA                  | I/O    | Serial LED data                                                                                                                                                     |

| Direct LED (LE                | D_MODE[1:0] must be       | set to | 11 to support direct LED mode)                                                                                                                                      |

| 113,112,111,<br>110,109,108,  | P0LINK_ACT~<br>P7LINK_ACT | 0      | Direct LED link/activity for port0~7                                                                                                                                |

| 107,106                       |                           |        | The LED should be connected to VDDIO_2 through a 220 ohm resistor.                                                                                                  |

| 103,102,101,<br>100,99,94,93, | P0SPD~<br>P7SPD           | 0      | Direct LED speed for port0~7                                                                                                                                        |

| 92                            | 731 5                     |        | The LED of P0SPD~P4SPD should be connected to VDDIO_2 through a 220 ohm resistor. The LED of P5SPD~P7SPD should be connected to VDDIO_3 through a 220 ohm resistor. |

|                               |                           |        | To support direct LED mode, MII port must be disabled by setting MII _PORT_EN to 0.                                                                                 |

| 91,90,87,84                   | P0DUP~                    | 0      | Direct LED duplex for port0~7                                                                                                                                       |

| 83,82,81,80                   | P7DUP                     |        | The LED should be connected to VDDIO_3 through a 220 ohm resistor.                                                                                                  |

|                               |                           |        | To support direct LED mode, MII port must be disabled by setting MII _PORT_EN to 0.                                                                                 |

# Pin description (continue)

| Pin No.                                   | Label     | Туре | Description                                                                                                                           |

|-------------------------------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| Miscellaneous                             |           |      |                                                                                                                                       |

| 119                                       | X1/OSCI   | I    | Crystal/ Oscillator 25MHz input                                                                                                       |

| 120                                       | X2        | 0    | Crystal output                                                                                                                        |

| 48                                        | RESETB    | I    | System reset (low active). Should be kept at "low" for at least 10 microseconds. The input voltage should be not higher than VDDIO_1. |

| 79                                        | INTR      | 0    | Interrupt output. Active low. The pin can be either active low or high by writing REG E7h[4]                                          |

| 116                                       | SCAN_MODE | I    | Scan mode for testing                                                                                                                 |

| 117                                       | TEST_MODE | I    | Test mode for testing                                                                                                                 |

| 20                                        | BGRES     | I    | Band gap reference voltage, it must be pull down by 6.19K ohm.                                                                        |

| Power & Ground                            | d         |      |                                                                                                                                       |

| 118,114,95,75,<br>49                      | VDDC      | Р    | 1.95V power for Core circuit                                                                                                          |

| 128,122,45,39,<br>33,27,21,19,<br>18,12,6 | VDDA      | Р    | 1.95V power for analog circuit                                                                                                        |

| 59                                        | VDDIO_1   | Р    | 1.95V power of I/O PAD of SS-SMII                                                                                                     |

| 104                                       | VDDIO_2   | Р    | 3.3V power of I/O PAD of link and speed LED                                                                                           |

| 88                                        | VDDIO_3   | Р    | 3.3V power for I/O PAD of speed, duplex LED and MII                                                                                   |

| 121,115,96,76,<br>50,47,46                | VSSC      | Р    | Core Ground                                                                                                                           |

| 125,42,36,30,<br>2415,9,3                 | VSSA      | Р    | Analog Ground                                                                                                                         |

| 105,89,60                                 | VSSIO     | Р    | I/O Ground                                                                                                                            |

Pin description (continue) latch in pins

| Pin No.  | iption (continue) late      |              | Description                                                                                                                                                                                             |  |

|----------|-----------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          |                             |              | -                                                                                                                                                                                                       |  |

| Power On | setting. The state of these | pins will    | be latched upon reset.                                                                                                                                                                                  |  |

| 53       | IPG_COMP_EN                 | IL, PU       | Enable IPG compensation 1: Enable (Default); 0: Disable The function can be set by writing register 01h[1:0]                                                                                            |  |

| 55       | BPDU_BCST_OFF               | IL, PU       | Filter the packet with MAC destination address 01-80-c2-00-00-03 ~01-80-c2-00-00-0F 1: Filter (Default) 0: Broadcast The function can be set by writing register 01h[2]                                 |  |

| 61,57    | WRR_SET1,<br>WRR_SET0       | IL, PD       |                                                                                                                                                                                                         |  |

|          |                             |              | 00= First in first out                                                                                                                                                                                  |  |

|          |                             |              | The function can be set by writing register 38h[15:0]                                                                                                                                                   |  |

| 66       | MII_MODE                    | IL, PU       | Reverse MII mode 0:Reverse MII (IP1717 works as a PHY) 1:Normal MII (IP1717 works as a MAC`) The function can be set by writing register E2h[2]                                                         |  |

| 69       | P16_FORCE_OFF               | IL, PU       | Port 16 force link 1: not force link(default) 0: force link The function can be set by writing register BDh[6] Port 16 only support 100M full duplex if port 16 force link and Reverse MII are enabled. |  |

| 71       | IGMP_EN                     | IL, PU       | IGMP enable 1: Disable GMP function (default) 0: Enable IGMP function The function can be set by writing register A5h[0]                                                                                |  |

| 64,73    | DRIVE1,<br>DRIVE0           | IL,PD,<br>PU | SS-SMII clock and data driving current setting                                                                                                                                                          |  |

|          | 51.117.20                   |              | TXCLK/TXSYNC   TXD                                                                                                                                                                                      |  |

| 87       | SLEW_RATE_OFF               | IL,PD        | Slew rate enable: 1: normal 0: fast (default) The function can be set by writing register EAh[5] If an external pull up resistor is used, it should be connected to VDDIO_3.                            |  |

# Pin description (continue) latch in pins

| Pin No.                                                               | Label                     | Туре   | Description                                                                                                                                                                                                                |  |  |

|-----------------------------------------------------------------------|---------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power On setting. The state of these pins will be latched upon reset. |                           |        |                                                                                                                                                                                                                            |  |  |

| 90                                                                    | TAG_PRI_ON                | IL,PD  | Tag priority enable: 1: enable 0: disable (default) The function can be set by writing register 17h[15:0]~18h[0]. If an external pull up resistor is used, it should be connected to VDDIO_3.                              |  |  |

| 91                                                                    | OQ_AGING_EN               | IL,PD  | Output queue aging time enable 1:enable 0: disable (default) The function can be set by writing register 39h[7] If an external pull up resistor is used, it should be connected to VDDIO_3.                                |  |  |

| 93,92                                                                 | PORT_PRI_1,<br>PORT_PRI_0 | IL,PD  | Port high priority enable setting  00: none (default)  10: port 13~16  The function can be set by writing register 14~15h[15:0] and 16h[1:0].  If an external pull up resistor is used, it should be connected to VDDIO_3. |  |  |

| 79                                                                    | MII_PORT_EN               | IL,PU  | MII port enable 1: MII port enable pin80~87,90~94 are changed to MII pins(default). 0:MII port disable pin80~87,90~94 are changed to LED pins.                                                                             |  |  |

| 97                                                                    | HOME_VLAN_OFF             | IL, PU | Home VLAN setting enable Port 0 ~ Port15 are all individual VLAN and only send to CPU port. 1: Disabled (Default) 0: Enabled                                                                                               |  |  |

| 112                                                                   | SS-SMII_TXC_DLY_<br>OFF   | IL,PU  | SS-SMII TXCLK delay 1: No delay (default) 0:delay 4ns The function can be set by writing register EAh[0]                                                                                                                   |  |  |

| 111                                                                   | SS-SMII_RXC_DLY_<br>OFF   | IL,PU  | SS-SMII RXCLK delay 1: No delay (default) 0:delay 4ns The function can be set by writing register EAh[1]                                                                                                                   |  |  |

| 110                                                                   | SS-SMII_RSYNC_DL<br>Y_OFF | IL,PU  | SS-SMII RXSYNC delay 1: No delay (default) 0:delay 4ns The function can be set by writing register EAh[2]                                                                                                                  |  |  |

| 108,109 | TRUNK_1,<br>TRUNK_0 | IL,PU | 11: none (default)                                                                       | 10:port 1~2<br>00: port 1~4 |

|---------|---------------------|-------|------------------------------------------------------------------------------------------|-----------------------------|

| 107     | X_ON_BK_ON          | IL,PU | Flow control off for full and half mode 1: flow control on (default) 0: flow control off |                             |

# Pin description (continue) latch in pins

| Pin No.       | Label                                                                 | Туре   | Description                                                                                                                                                                                                                            |  |