02/02/2017

## **High Power Factor Flyback LED Controller**

## with HV Start-up

### REV. 02

### **General Description**

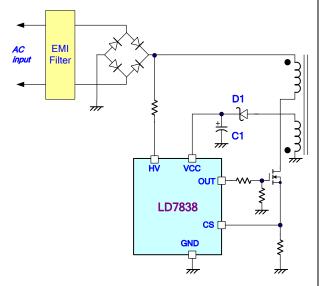

The LD7838 is a 700V HV start-up active PFC Flyback controller, specially designed for LED lighting application. This device operates in transition or boundary mode and integrates with completed protections required. It minimizes the components counts in either SOP-7 package. Those make it easy to design with for cost-effective applications.

With High Voltage start-up technology, power factor correction and boundary mode switching control, the start-up time and resistor loss could be minimized efficiently. The circuit can easily achieve power factor is upper 0.92 to meet most of the international requirements as IEC61000-3-2 standard certifications.

With completed protection built inside this IC, such as over voltage protection (OVP), over current protection (OCP), over load protection (OLP), over temperature protection (OTP), and short circuit protection (SCP), pin open / short protection. It enables the circuit to meet most safety requirements in both normal and abnormal test

### **Features**

- High voltage (700V) startup circuit by HV pin for 85~305V<sub>AC</sub> input range

- High Power Factor (> 0.92)

- High-efficiency Transition mode operation

- Lower Power Saving ( < 0.5W)

- Accurate OLP Compensation for High/ Low Line

- Built in BNI/ BNO Function

- Wide UVLO (16Von and 8 Voff) range

- Built in VCC Over Voltage Protection

- Built in Over Load Protection

- Adjustable Over Output Current Protection (Cycle by Cycle Current Limiting)

- Internal Over temperature protection

### **Applications**

- Lighting Driver module

- Active Power Factor Correction Power Supply

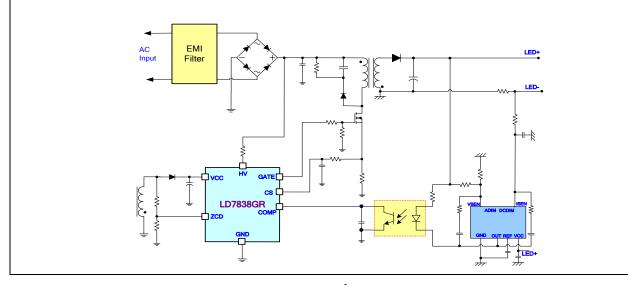

### **Typical Application**

Leadtrend Technology Corporation www.leadtrend.com.tw LD7838-DS-02 February 2017

02/02/2017

## **Pin Configuration**

Year code WW: Week code Production code

## **Ordering Information**

| Part number | Package | Top Mark  | Shipping          |

|-------------|---------|-----------|-------------------|

| LD7838      | SOP-7   | LD7838 GR | 2500 /tape & reel |

YY:

PP:

The LD7838 is ROHS compliant/ green packaged.

## **Protection Mode**

| Part number | BNI/BNO | VCC_OVP       | ZCD_OVP       | OLP/<br>output Short | Output diode<br>Short |

|-------------|---------|---------------|---------------|----------------------|-----------------------|

| LD7838      | Yes     | Auto recovery | Auto recovery | Auto recovery        | Auto recovery         |

## **Pin Descriptions**

| Pin | NAME | FUNCTION                                                                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZCD  | Quasi resonance detector and programmable maximum ON-time.                                                                                                                                                        |

| 2   | COMP | Feedback pin. Connect a photo-coupler to close the control loop to achieve regulation.                                                                                                                            |

| 3   | CS   | Current sense pin, connect it to sense the MOSFET current for OCP                                                                                                                                                 |

| 4   | GND  | Ground                                                                                                                                                                                                            |

| 5   | OUT  | Gate drive output to drive the external MOSFET                                                                                                                                                                    |

| 6   | VCC  | Power source VCC pin                                                                                                                                                                                              |

| 8   | HV   | Connect this pin to positive terminal of main bulk cap to provide the startup current for controller. When Vcc is UVLO on, the HV loop will open and turn off internal current source to minimize the power loss. |

02/02/2017

Leadtrend Technology Corporation www.leadtrend.com.tw LD7838-DS-02 February 2017

02/02/2017

### **Absolute Maximum Ratings**

| Supply Voltage, VCC                                      | -0.3V~30V       |

|----------------------------------------------------------|-----------------|

| High voltage pin, HV                                     | -0.3V~700V      |

| OUT                                                      | -0.3V~VCC +0.3V |

| COMP, ZCD,CS                                             | -0.3V~6V        |

| Maximum Junction Temperature                             | 150°C           |

| Storage Temperature Range                                | -65°C ~ 150°C   |

| Package Thermal Resistance (SOP-7, $\theta_{JA}$ )       | 160°C/W         |

| Power Dissipation (SOP-7, at Ambient Temperature = 85°C) | 250mW           |

| Lead temperature (Soldering, 10sec)                      | 260°C           |

| ESD Voltage Protection, Human Body Model (Except HV pin) | 2.5KV           |

| ESD Voltage Protection, Machine Model                    | 250 V           |

|                                                          |                 |

#### Caution:

Stress exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stress above Recommended Operating Conditions may affect device reliability.

### **Recommended Operating Conditions**

| Item                           | Min. | Max. | Unit |

|--------------------------------|------|------|------|

| Supply VCC Voltage             | 9.5  | 27.5 | V    |

| VCC pin capacitor              | 4.7  | 22   | μF   |

| Operating Junction Temperature | -40  | 125  | °C   |

| Comp pin capacitor             | 0.22 | 4.7  | μF   |

| CS pin filter capacitance      | 100  | 680  | pF   |

| CS pin filter resistance       | 100  | 2k   | Ω    |

Note:

- 1. It's essential to connect VCC pin with a SMD ceramic capacitor  $(0.1\mu$ F~ $0.47\mu$ F) to filter out the undesired switching noise for stable operation. This capacitor should be placed close to IC pin as possible.

- 2. The VCC capacitor is only for IC used and cannot parallel with other devices.

- 3. Connecting a capacitor to COMP pin is also essential to filter out the undesired switching noise for stable operation.

- 4. The small signal components should be placed close to IC pin as possible.

02/02/2017

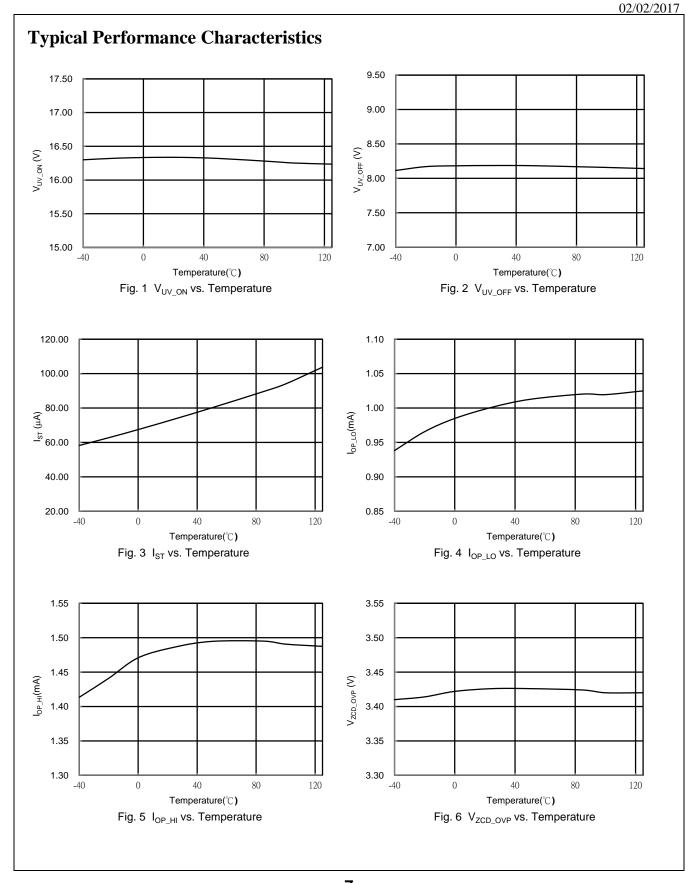

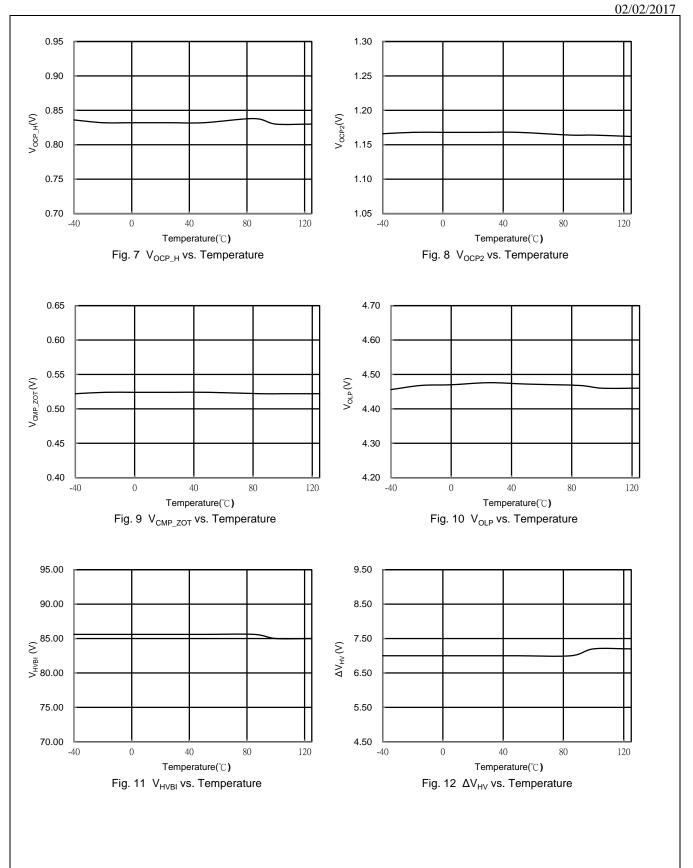

### **Electrical Characteristics**

(V<sub>CC</sub>=15.0V,  $T_A = 25^{\circ}C$  unless otherwise specified.)

| PARAMETER                          | CONDITIONS                                            | SYMBOL                | MIN  | ТҮР  | MAX  | UNITS           |

|------------------------------------|-------------------------------------------------------|-----------------------|------|------|------|-----------------|

| High voltage Supply(HV Pin         | )                                                     |                       |      |      |      |                 |

| High-voltage current Source        | HV = 180 V <sub>DC</sub><br>V <sub>CC</sub> = 4V      | $I_{HV}$              | 1.5  | 1.8  | 2.1  | mA              |

| Off-state Leakage current          | $V_{CC}$ > $V_{UV_{ON}}$ ,HV=500 $V_{DC}$             | I <sub>HV_OFF</sub>   |      |      | 30   | μA              |

| Brown-in Level                     | $V_{CC} > V_{UV_{ON}}, ZCD = 0$                       | V <sub>HVBI</sub>     |      | 90   | 100  | V <sub>DC</sub> |

| HV Pin Hysteresis                  | V <sub>HVBI</sub> - V <sub>HVBO</sub>                 | $\Delta V$ HV         |      | 10   |      | V <sub>DC</sub> |

| Supply Voltage (VCC Pin)           |                                                       | · ·                   |      |      |      |                 |

| Startup Current                    | $V_{CC} < V_{UV_ON}$                                  | I <sub>ST</sub>       |      | 75   | 95   | μA              |

|                                    | $V_{COMP} = 0V, ZCD = 0$                              | I <sub>OP_LO</sub>    |      | 1    |      | mA              |

| Operating Current                  | $V_{COMP} = 3V, ZCD = 0$                              | I <sub>OP_HI</sub>    |      | 1.5  |      | mA              |

| (with 1nF load on OUT pin)         | V <sub>CC</sub> / ZCD OVP, OLP, CS short, Diode short | I <sub>OP_PRO</sub>   |      | 0.3  |      | mA              |

| UVLO (OFF)                         |                                                       | $V_{UV\_OFF}$         | 7    | 8    | 9    | V               |

| UVLO (ON)                          |                                                       | V <sub>UV_ON</sub>    | 15   | 16   | 17   | V               |

| HV Self Bias                       |                                                       | V <sub>LDO_LO</sub>   | 9.1  | 9.8  | 10.5 | V               |

| De-Latch VCC Voltage               | PDR( Power Down Reset)                                | V <sub>PDR</sub>      | 6.8  | 7.5  | 8.2  | V               |

| VCC OVP Level                      |                                                       | V <sub>CC_OVP</sub>   | 27   |      | 29   | V               |

| VCC/ ZCD OVP De-bounce<br>Time     |                                                       |                       |      | 250  |      | μs              |

| Voltage Feedback(Comp Pir          | n)                                                    |                       |      |      |      |                 |

| Short circuit current              | V <sub>COMP</sub> =0                                  | I <sub>COMP</sub>     | 0.4  | 0.5  | 0.6  | mA              |

| Open loop voltage                  |                                                       | $V_{CMP\_OPEN}$       | 5.0  |      | 5.8  | V               |

| Over load protection Trip<br>Level |                                                       | V <sub>OLP</sub>      | 4.45 | 4.6  | 4.75 | V               |

| Zara ON time Threshold             | Into the burst mode                                   | V <sub>CMP_ZOTL</sub> | 0.46 | 0.5  | 0.56 | V               |

| Zero ON-time Threshold             | Out off the burst mode                                | V <sub>CMP_ZOTH</sub> | 0.49 | 0.53 | 0.57 | V               |

| Over load protection Delay<br>Time | *                                                     | T <sub>DEB_OLP</sub>  |      | 285  |      | ms              |

5

02/02/2017

| PARAMETER CONDITIONS                       |                                                 | SYMBOL                | MIN  | TYP  | MAX  | UNITS   |

|--------------------------------------------|-------------------------------------------------|-----------------------|------|------|------|---------|

| Zero Current Detector (ZCD                 | Pin)                                            |                       |      |      |      |         |

| Upper Clamp Voltage                        | Ι <sub>DET</sub> =100μΑ                         | $V_{ZH}$              | -    | 4.7  | -    | V       |

| Lower Clamp Voltage                        | I <sub>DET=</sub> -2mA                          | $V_{ZL}$              | 0    |      | -0.3 | V       |

|                                            |                                                 | V <sub>ZCD</sub>      | 0.15 | 0.2  | 0.25 | V       |

| Input Voltage Threshold                    | Hysteresis                                      | VH <sub>ZCD</sub>     |      | 0.1  |      | V       |

| Input bias current                         | V <sub>ZCD</sub> =1V~4V, OUT is Low level       | I <sub>ZCD_BIAS</sub> | 0.0  |      | 1.0  | μA      |

| ZCD OVP Threshold                          |                                                 | V <sub>ZCD_OVP</sub>  | 3.3  | 3.5  | 3.7  | V       |

| ZCD OVP De-bounce                          | *                                               | T <sub>DEB_OVP</sub>  |      | 250  |      | μs      |

| Minimum (ON+OFF)-Time                      |                                                 |                       |      |      |      |         |

| Minimum (ON+OFF)-Time                      | Fmax(300kHz),                                   | T <sub>F_MAX</sub>    |      | 3.3  |      | μS      |

| Gate Drive Output (OUT Pin                 |                                                 |                       |      |      |      |         |

| Output Low Level                           | V <sub>CC</sub> =15V, I <sub>SINK</sub> =20mA   | $V_{G_{LO}}$          | 0    |      | 0.5  | V       |

| Output High Level                          | V <sub>CC</sub> =15V, I <sub>SOURCE</sub> =20mA | $V_{G_{HI}}$          | 10   |      | 14   | V       |

| Rising Time                                | V <sub>CC</sub> =15V, CL=1000pF(*)              | $T_{G_{RISE}}$        |      | 250  |      | ns      |

| Falling Time                               | V <sub>CC</sub> =15V, CL=1000pF(*)              | $T_{G_FALL}$          |      | 50   |      | ns      |

| Current Sensing (CS Pin)                   |                                                 |                       |      |      |      |         |

| Soft Start Time                            | *                                               |                       |      | 10   |      | ms      |

| Leading edge blanking time                 | *                                               |                       |      | 425  |      | ns      |

| Over Current Limit                         |                                                 | V <sub>OCP_H</sub>    | 0.8  | 0.85 | 0.9  | V       |

| OCP Compensation Current                   | I <sub>OCP</sub> =1/500K*HV                     | I <sub>OCP</sub>      | 170  | 200  | 220  | μΑ/100V |

| Current Limit-2 for diode short protection |                                                 | V <sub>OCP2</sub>     | 1    | 1.2  | 1.4  | V       |

| Delay Time of Diode Short<br>Protection    | *                                               | T <sub>DEB_DSP</sub>  |      | 7    |      | Times   |

| Internal OTP (Over Temp. P                 | rotection)                                      |                       |      | •    |      | •       |

| OTP Trip level                             | *                                               |                       |      | 140  |      | °C      |

| OTP Hysteresis                             | *                                               |                       |      | 30   |      | °C      |

6

Note: <sup>(\*)</sup> Guaranteed by Design.

### Leadtrend Technology Corporation www.leadtrend.com.tw LD7838-DS-02 February 2017

8

LD7838

## Application Information Operation Overview

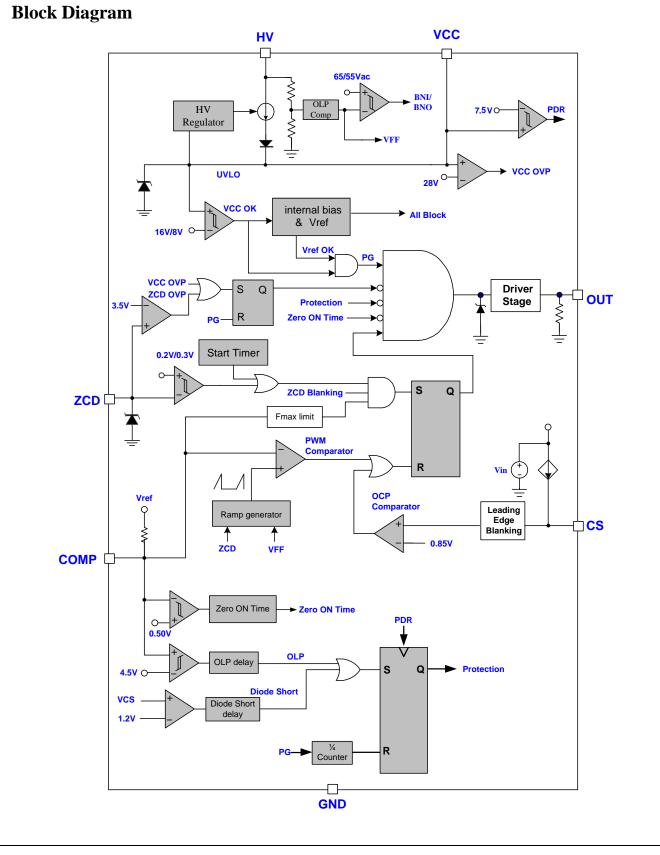

The LD7838 is a 700V HV start-up active PFC Flyback controller for LED lighting applications. It integrates more functions to reduce the external components counts and the size. Its major features are described as below.

The LD7838 is a voltage-mode TM PFC controller. The turn-on time of the switch is fixed while the turn-off time is varied in steady state. Therefore, the switching frequency varies in accordance with the input voltage variation. The LD7838 features over load protection, over voltage protection, over current protection, under voltage lockout and leading edge blinking time of the current sensing. Also, the LD7838 requires no mains voltage sensing unlike what the other traditional current mode PFC controllers behave for power saving.

# Internal High-Voltage Startup Circuit and Under Voltage Lockout (UVLO)

The traditional circuit provides the startup current through a startup resistor to power up the PWM controller. However, it consumes significant power to meet the power saving requirement. In most cases, startup resistors carry large resistance. And, a larger resistor will spend more time to start up.

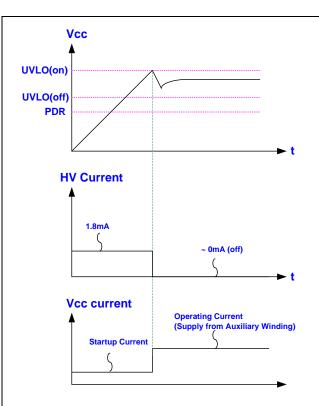

To achieve optimized topology, as shown in Fig. 13, LD7838 is implemented with a high-voltage startup circuit to enhance it. During startup, a high-voltage current source sinks current from the full-bridge rectifier to provide the startup current and charge Vcc capacitor C1 at the same time. On condition of VCC below UVLO(ON), the charge current will increases to 1.8mA once V<sub>CC</sub> rises above UVLO(ON) voltage threshold during start up. Meanwhile, it consumes only 75 $\mu$ A for V<sub>CC</sub> supply current, that most of the HV current is

reserved to charge the  $V_{CC}$  capacitor. In using such configuration, the turn-on delay time will be almost no difference either in low-line or high-line conditions.

LD7838

Once the  $V_{CC}$  voltage rises higher than UVLO(on) to power on the LD7838 and further to deliver the gate drive signal, the high-voltage current source will be disabled and the supply current is provided from the auxiliary winding of the transformer. Therefore, it would eliminate the power loss on the startup circuit and perform highly power saving.

An UVLO comparator is embedded to detect the voltage on the Vcc pin to ensure the supply voltage enough to power on the LD7838 PWM controller and in addition to drive the power MOSFET. As shown in Fig. 14, a hysteresis is provided to prevent the shutdown from the voltage dip during startup.

Fig. 13 High voltage start up circuit

Fig. 14 High voltage start up sequence

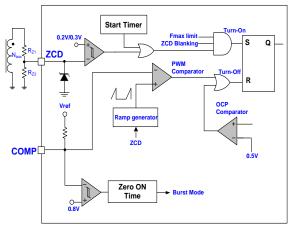

# Ramp Generator Block and Zero Current Detection (ZCD)

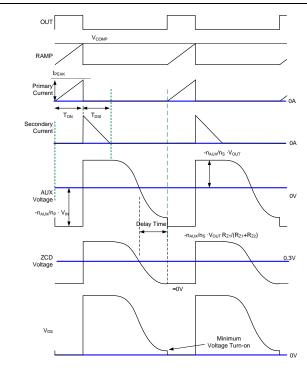

Fig. 15 shows typical ramp generator block and ZCD block. The comp pin voltage and the output of the ramp generator block are compared to determine the MOSFET ON-time, as shown in Fig. 16.

A greater comp voltage produces more ON-time. Using an external resistor connected to ZCD pin to set the desired slope of the internal ramp, the user may program the maximum ON-time. Alternatively, the ON-time will also achieve its maximum when COMP pin voltage trip OLP trigger point.

The maximum ON-time should be set according to the condition of the transformer, lowest AC line voltage, and maximum output power. A choice of optimum resistor value would result in best performance.

Leadtrend Technology Corporation www.leadtrend.com.tw LD7838-DS-02 February 2017

10

# LD7838

#### 02/02/2017

It shuts down the drive output if COMP pin voltage falls below zero ON-time threshold. This optimizes the efficiency in power saving in most conditions.

The Zero Current Detection block will detect auxiliary winding signal to drive MOSFET as ZCD pin voltage drops to 0.2V. As ZCD pin voltage drop to 0.2V, the current through the transformer is below zero. This feature enables transition-mode operation. The ZCD comparator would not operate if ZCD pin voltage remains at above 0.3V. Once it drops below 0.2V, the zero current detector will act to turn on the MOSFET.

Fig. 15

Fig. 16 shows typical ZCD-related waveforms. Since ZCD pin carries some capacitance, it produces some delay to the turn-on time caused from Rz1. During delay time, the junction capacitor of the MOSFET resonates with the primary inductor of the transformer and the drain-source voltage ( $V_{DS}$ ) decreases accordingly. So, the MOSFET consumes less voltage to turn on and it therefore minimizes the power dissipation.

The LD7838 features Burn-in/out function on HV pin. As the built-in comparator detects the DC voltage half wave rectify line voltage condition, it will shut off the controller to prevent from any damage. When  $V_{HV} < V_{HVBO}$ , the gate output will remain off even when the Vcc already reaches UVLO(oN). It therefore forces the Vcc hiccup between UVLO(oN) and UVLO(OFF). Unless the line voltage rises over  $V_{HVBI}$ , the gate output will not start switching even as the next UVLO(oN) is tripped. A hysteresis is implemented to prevent the false-triggering during turn-on and turn-off.

### **Programming Maximum ON-time**

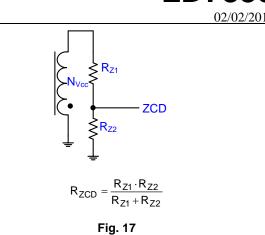

LD7838 features adjustable maximum ON-time to limit power output in abnormal operation. The selection of maximum ON-time is subject to ZCD resistance as shown in Fig. 17. ZCD resistance can be obtained from below:

The following table is a suggestion for maximum ON-time setting.

| в                                 | Max. Ton | R <sub>zcd</sub> |  |

|-----------------------------------|----------|------------------|--|

| R <sub>ZCD</sub>                  | (Тур.)   | Suggestion       |  |

| 44.65k $\leq$ R <sub>ZCD</sub>    | 25µs     | <b>47</b> kΩ     |  |

| $25.65k \leq R_{ZCD} \leq 28.35k$ | 20µs     | <b>27k</b> Ω     |  |

| $13.3k \leq R_{ZCD} \leq 14.7k$   | 16µs     | 14k $\Omega$     |  |

| $R_{ZCD} \leq 6.3k$               | 10µs     | <b>6k</b> Ω      |  |

#### Output OVP on ZCD

When the LED string open circuit occurs, the reflected output voltage of aux winding will cause ZCD voltage up. If the ZCD voltage runs up to 3.5V, LD7838 will enforce the gate off until the 2nd cycle of Vcc hiccup is tripped, The selection of output over voltage (V<sub>OVP</sub>)trigger level is subject to ZCD divide resistance as the below equation:

$$V_{OVP} \times \frac{N_{VCC}}{N_S} \times \frac{R_{Z2}}{R_{Z1} + R_{Z2}} = 3.5V$$

#### **Output Drive Stage**

11

With typical 125mA/-500mA driving capability, an output stage of a CMOS buffer is incorporated to drive a power MOSFET directly. The output voltage is clamped at

13V to protect the MOSFET gate even when the VCC voltage is higher than 13V.

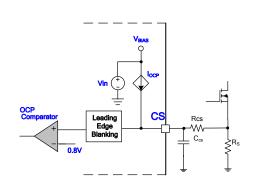

# Current Sensing and Leading-edge Blanking

The LD7838 detects the primary MOSFET current from the CS pin, which is for the pulse-by-pulse current limit. The maximum voltage threshold of the current sensing pin is set at 0.85V. From above, the MOSFET peak current can be obtained from below.

$$I_{PEAK(MAX)} = \frac{0.85V}{R_s}$$

A leading-edge blanking (LEB) time is included in the input of CS pin to prevent the false-trigger from the current spike. In the low power application, if the total pulse width of the turn-on spikes is less than and the negative spike on the CS pin doesn't exceed -0.3V, it could eliminated the R-C filter.

However, the total pulse width of the turn-on spike is determined by the output power, circuit design and PCB layout. It is strongly recommended to adopt a smaller R-C filter for higher power application to avoid the CS pin being damaged by the negative turn-on spike.

### Adjustable OCP Compensation

In general, the power converter can deliver more current at high input voltage than at low input voltage. To compensate this, an offset voltage is added to the CS signal by an internal current source (IOCP) and an external resistor ( $R_{CS}$ ) in series between the sense resistor (Rs) and the CS pin, as shown in Fig. 18.

#### Fig. 18 Current sense for over current protection

By selecting a proper value of the resistor in series with the CS pin, the amount of compensation can be adjusted.

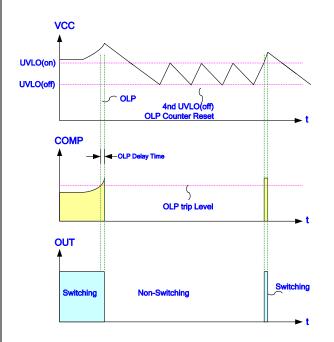

# Over Load Protection (OLP) - Auto Recovery

To protect the circuit from damage due to overload condition or output short condition, a smart OLP function is implemented in the LD7838 for it. The OLP function is an auto-recovery type protection. Fig. 19 shows the waveforms of the OLP operation. Under such fault condition, the feedback system will force the voltage loop toward saturation and thus pull up the voltage of COMP pin (VCOMP). If the VCOMP trips the OLP threshold of 4.5V and stays for over OLP delay time, the protection will be activated to turn off the gate output and to shut down the switching of power circuit. The OLP delay time is to prevent the false-trigger during the power-on and turn-off transient.

A divided-by-4 counter is implemented to reduce the average power consumption under OLP behavior.

Whenever OLP is activated, the output is latched off and the divided-by-4 counter starts to count the number of UVLO(off). The latch will be released if the 4nd UVLO(off) point is counted, and then the output recovers switching again.

12

By using such protection mechanism, the average input power can be reduced to a very low level so that the component temperature and stress can be controlled within a safe operating area.

#### Fig. 19 Over load protection sequence

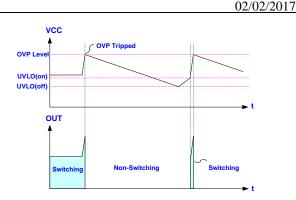

### **OVP (Over Voltage Protection) on Vcc**

The maximum rating of the VCC pin is limited below 29V. To prevent VCC from the fault condition, the LD7838 is implemented with OVP function on Vcc pin. As soon as the Vcc voltage is over OVP threshold voltage, the output gate drive circuit will be shutdown simultaneously thus to stop the switching of the power MOSFET until the next UVLO(on). The Vcc over voltage function of the LD7838 is an auto-recovery protection. The Fig. 20 shows its operation. Upon removal of the OVP condition will resume the Vcc level and the output operation

LD7838

Fig. 20 Over voltage protection on VCC pin

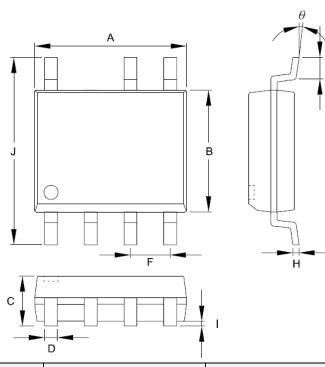

### **Package Information** SOP-7

|         | Dimensions i | n Millimeters | Dimensio | ns in Inch |

|---------|--------------|---------------|----------|------------|

| Symbols | MIN          | МАХ           | MIN      | МАХ        |

| А       | 4.801        | 5.004         | 0.189    | 0.197      |

| В       | 3.810        | 3.988         | 0.150    | 0.157      |

| С       | 1.346        | 1.753         | 0.053    | 0.069      |

| D       | 0.330        | 0.508         | 0.013    | 0.020      |

| F       | 1.194        | 1.346         | 0.047    | 0.053      |

| н       | 0.178        | 0.254         | 0.007    | 0.010      |

| I       | 0.102        | 0.254         | 0.004    | 0.010      |

| J       | 5.791        | 6.198         | 0.228    | 0.244      |

| М       | 0.406        | 1.270         | 0.016    | 0.050      |

| θ       | 0°           | 8°            | 0°       | 8°         |

### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

M

02/02/2017

## **Revision History**

| REV. | Date       | Change Notice                                                                                                                                                                                                                                                                                  |  |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00   | 10/31/2016 | Original Specification.                                                                                                                                                                                                                                                                        |  |

| 01   | 11/22/2016 | Update EC table                                                                                                                                                                                                                                                                                |  |

| 02   | 02/02/2017 | <ol> <li>Update the maximum ON-time setting table on page 11</li> <li>Add limited value of Zero ON-time Threshold on page 5</li> <li>Update recommend operation condition of CS pin filter resistance on page 4</li> <li>Add limitation value of OCP Compensation Current on page 6</li> </ol> |  |