### **General Description**

The MAX44265 op amp features a maximized ratio of gain bandwidth (GBW) to supply current and is ideal for battery-powered applications such as handsets, tablets, notebooks, and portable medical equipment. This CMOS op amp features an ultra-low input-bias current of 1pA, rail-to- rail input and output, low supply current of 4µA, and operates from a single 1.8V to 5.5V supply. For additional power conservation, the IC also features a low-power shutdown mode that reduces supply current to 1nA and puts the amplifier's outputs in a high-impedance state. This device is unity-gain stable with a 200kHz GBW product.

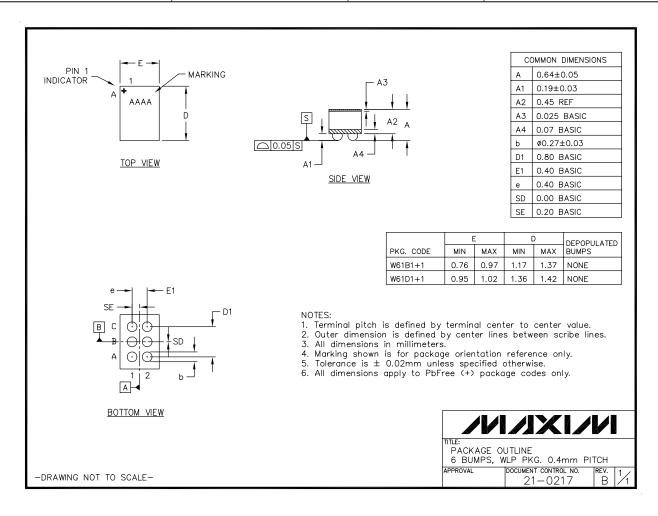

It is available in a space-saving, 0.9mm x 1.3mm, 6-bump WLP package and is specified over the -40°C to +85°C extended operating temperature range.

### **Applications**

Cell Phones Tablet/Notebook Computers Mobile Accessories **Battery-Powered Devices**

### **Features**

- ♦ 200kHz GBW

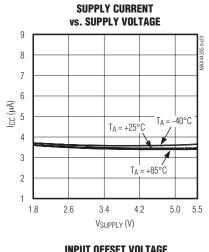

- ♦ Ultra-Low 4µA Supply Current

- ♦ Single 1.8V to 5.5V Supply Voltage Range

- ♦ Ultra-Low 1pA Input Bias Current

- ♦ Rail-to-Rail Input and Output Voltage Ranges

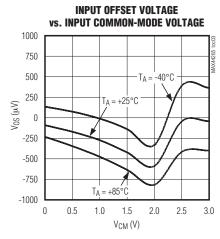

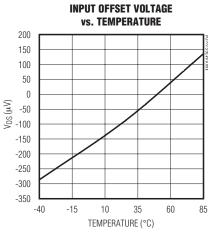

- ♦ Low ±200µV Input Offset Voltage

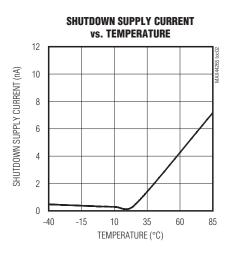

- ♦ Low 0.001µA Shutdown Current

- **♦** High-Impedance Output During Shutdown

- ♦ Unity-Gain Stable

- ♦ Available in a Tiny, 0.9mm x 1.3mm, 6-Bump WLP **Package**

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|----------------|-----------------|-------------|

| MAX44265EWT+ | -40°C to +85°C | 6 WLP           | +BY         |

#### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage (VDD to VSS)0.3V to +6.0V        | Operating Temperature Range40°C to +85°C |

|-------------------------------------------------------|------------------------------------------|

| IN_+, IN, OUT_, SHDN(VSS - 0.3V) to (VDD + 0.3V)      | Junction Temperature+150°C               |

| Current into IN +, IN±20mA                            | Storage Temperature Range65°C to +150°C  |

| Output Short-Circuit Duration to VDD or Vss           | Soldering Temperature (reflow)+260°C     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                          |

| 6-Bump WLP (derate 10.5mW/°C above +70°C) 840mW       |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, V_{CM} = 0V, V_{OUT} = V_{DD}/2, R_L = \infty \text{ connected to } V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS                                                                                                       |                    | MIN                   | TYP   | MAX                   | UNITS |

|------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------|-----------------------|-------|

| Supply Voltage Range         | V <sub>DD</sub> | Guaranteed by PSRR test                                                                                          |                    | 1.8                   |       | 5.5                   | V     |

|                              |                 | V <sub>DD</sub> = 1.8V                                                                                           |                    |                       | 4     |                       |       |

| Supply Current               | IDD             | $V_{DD} = 5.5V$                                                                                                  |                    |                       | 4     | 5.0                   | μΑ    |

| Shutdown Supply Current      | IDD(SHDN_)      | SHDN_ = GND                                                                                                      |                    |                       | 0.001 | 0.5                   | μΑ    |

| Input Offset Voltage         | Vos             |                                                                                                                  |                    |                       | ±0.2  | ±1                    | mV    |

| Input Bias Current           | IB              | (Note 2)                                                                                                         |                    |                       | ±1    | ±10                   | рА    |

| Input Offset Current         | Ios             | (Note 2)                                                                                                         |                    |                       | ±1    | ±10                   | рА    |

| Input Desistance             | Dur             | Common mode                                                                                                      |                    |                       | 1     |                       | 00    |

| Input Resistance             | R <sub>IN</sub> | Differential mode, -1mV < V <sub>IN</sub> < +1mV                                                                 |                    |                       | 10    |                       | GΩ    |

| Input Common-Mode Range      | V <sub>CM</sub> | Guaranteed by CMRR test                                                                                          |                    | V <sub>SS</sub> - 0.1 |       | V <sub>DD</sub> + 0.1 | V     |

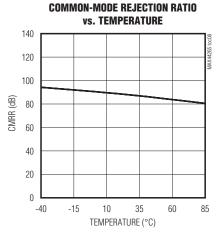

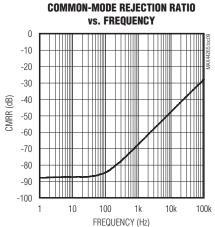

| Common-Mode Rejection Ratio  | CMRR            | -0.1V < V <sub>CM</sub> < V <sub>DD</sub> + 0.1V, V <sub>DD</sub> = 5.5V                                         |                    | 70                    | 80    |                       | dB    |

| Power-Supply Rejection Ratio | PSRR            | 1.8V < V <sub>DD</sub> < 5.5V                                                                                    |                    | 65                    | 95    |                       | dB    |

|                              |                 | 25mV < V <sub>OUT</sub> < V <sub>DD</sub> - $25$ mV,<br>R <sub>L</sub> = $100$ kΩ, V <sub>DD</sub> = $5.5$ V     |                    | 95                    | 120   |                       | 10    |

| Open-Loop Gain               | Avol            | 100mV $<$ V <sub>OUT</sub> $<$ V <sub>DD</sub> - 100mV,<br>R <sub>L</sub> = 5k $\Omega$ , V <sub>DD</sub> = 5.5V |                    | 95                    | 110   |                       | dB    |

|                              |                 |                                                                                                                  | $R_L = 100k\Omega$ |                       | 2.5   | 5                     |       |

| Output-Voltage-Swing High    | Voh             | V <sub>DD</sub> - V <sub>OUT</sub>                                                                               | $R_L = 5k\Omega$   |                       | 50    | 70                    | mV    |

|                              |                 |                                                                                                                  | $R_L = 1k\Omega$   |                       | 250   |                       |       |

| Output-Voltage-Swing Low     |                 |                                                                                                                  | $R_L = 100k\Omega$ |                       | 2.5   | 5                     |       |

|                              | V <sub>OL</sub> | Vout - Vss                                                                                                       | $R_L = 5k\Omega$   |                       | 50    | 70                    | mV    |

|                              |                 |                                                                                                                  | $R_L = 1k\Omega$   |                       | 250   |                       |       |

| Output Short-Circuit Current | IOUT(SC)        | <u>'</u>                                                                                                         |                    |                       | ±15   |                       | mA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, V_{CM} = 0V, V_{OUT} = V_{DD}/2, R_L = \infty \text{ connected to } V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                                                                               |                                          | MIN | TYP   | MAX | UNITS  |  |

|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-------|-----|--------|--|

| CLIDAL Lagia Laur                            | \/                | $V_{DD} = 1.8V \text{ to } 3.6V$                                                                                         |                                          |     |       | 0.4 | V      |  |

| SHDN_ Logic Low                              | VIL               | $V_{DD} = 3.6V \text{ to } 5$                                                                                            | V <sub>DD</sub> = 3.6V to 5.5V           |     |       | 0.8 | v      |  |

| CLIDAL Lagia High                            | \/                | $V_{DD} = 1.8V \text{ to } 3$                                                                                            | .6V                                      | 1.4 |       |     | - V    |  |

| SHDN_ Logic High                             | V <sub>IH</sub>   | $V_{DD} = 3.6V \text{ to } 5$                                                                                            | .5V                                      | 2   |       |     |        |  |

| GUDN Insert Birs Ormant                      | IJЦ               | SHDN_ = V <sub>SS</sub> (1                                                                                               | Note 2)                                  |     |       | 1   | A      |  |

| SHDN_ Input Bias Current                     | l <sub>IH</sub>   | SHDN_ = V <sub>DD</sub>                                                                                                  |                                          |     |       | 500 | nA     |  |

| Output Leakage in Shutdown                   | IOUT(SHDN_)       | SHDN_ = V <sub>SS</sub> , \                                                                                              | / <sub>OUT</sub> = 0V to V <sub>DD</sub> |     | 1     | 500 | nA     |  |

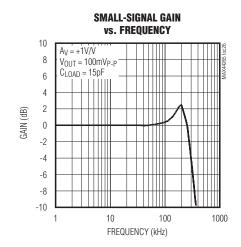

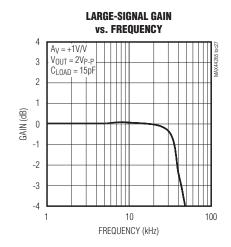

| Gain-Bandwidth Product                       |                   |                                                                                                                          |                                          |     | 200   |     | kHz    |  |

| Slew Rate                                    |                   |                                                                                                                          |                                          |     | 0.1   |     | V/µs   |  |

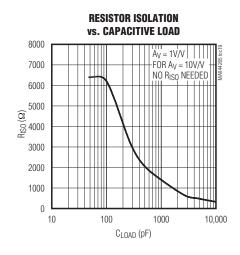

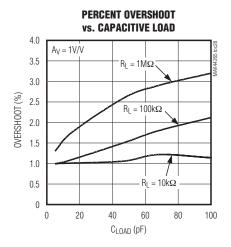

|                                              | C <sub>LOAD</sub> | No sustained oscillations                                                                                                | $A_V = 1V/V$                             |     | 30    |     |        |  |

| Capacitive-Load Stability (See               |                   |                                                                                                                          | $A_V = 10V/V$                            |     | 250   |     |        |  |

| the <i>Driving Capacitive Loads</i> Section) |                   |                                                                                                                          | $R_L = 5k\Omega$ , $A_V = 1V/V$          |     | 200   |     | pF     |  |

|                                              |                   |                                                                                                                          | $R_{ISO} = 1k\Omega$ , $A_V = 1V/V$      |     | 100   |     | 1      |  |

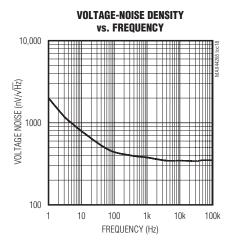

| Input Voltage-Noise Density                  |                   | f = 1kHz                                                                                                                 |                                          |     | 400   |     | nV/√Hz |  |

| Input Current-Noise Density                  |                   | f = 1kHz                                                                                                                 |                                          |     | 0.001 |     | pA/√Hz |  |

| Settling Time                                |                   | To 0.1%, V <sub>OUT</sub> = 2V step, A <sub>V</sub> = -1V/V                                                              |                                          |     | 18    |     | μs     |  |

| Delay Time to Shutdown                       | tsн               | I <sub>DD</sub> = 5% of normal operation,<br>V <sub>DD</sub> = 5.5V, V <sub>SHDN</sub> = 5.5V to 0 step                  |                                          |     | 2     |     | μs     |  |

| Delay Time to Enable                         | tEN               | V <sub>OUT</sub> = 2.7V, V <sub>OUT</sub> settles to 0.1%,<br>V <sub>DD</sub> = 5.5V, V <sub>SHDN</sub> = 0 to 5.5V step |                                          |     | 30    |     | μs     |  |

| Power-Up Time                                |                   | $V_{DD} = 0 \text{ to } 5.5V$                                                                                            | step                                     |     | 5     |     | μs     |  |

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, V_{CM} = 0V, V_{OUT} = V_{DD}/2, R_L = \infty \text{ connected to } V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                    | SYMBOL            | CONDITIONS              | MIN | TYP | MAX | UNITS |

|----------------------------------------------|-------------------|-------------------------|-----|-----|-----|-------|

| Supply Voltage Range                         | V <sub>DD</sub>   | Guaranteed by PSRR test | 1.8 |     | 5.5 | V     |

| Supply Current                               | I <sub>DD</sub>   | V <sub>DD</sub> = 5.5V  |     |     | 5.5 | μΑ    |

| Shutdown Supply Current                      | IDD(SHDN_)        | SHDN_ = GND             |     |     | 1   | μΑ    |

| Input Offset Voltage                         | Vos               |                         |     |     | ±5  | mV    |

| Input-Offset-Voltage Temperature Coefficient | TC <sub>VOS</sub> |                         |     | ±5  |     | μV/°C |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.8V \text{ to } 5.5V, V_{SS} = 0V, V_{CM} = 0V, V_{OUT} = V_{DD}/2, R_L = \infty \text{ connected to } V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                       | SYMBOL          | CONDITIONS                                                                                                   |                                                                    | MIN | TYP | MAX                    | UNITS |

|---------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------------------------|-------|

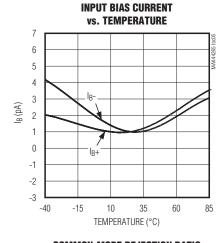

| Input Bias Current              | IB              |                                                                                                              |                                                                    |     |     | ±30                    | рΑ    |

| Input Offset Current            | los             |                                                                                                              |                                                                    |     |     | ±20                    | рΑ    |

| Input Common-Mode Range         | Vсм             | Guaranteed by CMR                                                                                            | Guaranteed by CMRR test                                            |     |     | V <sub>DD</sub> + 0.05 | V     |

| Common-Mode Rejection Ratio     | CMRR            | -0.05V < V <sub>CM</sub> < V <sub>DD</sub>                                                                   | $+ 0.05V, V_{DD} = 5.5V$                                           | 60  |     |                        | dB    |

| Power-Supply Rejection Ratio    | PSRR            | 1.8V < V <sub>DD</sub> < 5.5V                                                                                |                                                                    | 59  |     |                        | dB    |

|                                 | Δνω             | 25mV < V <sub>OUT</sub> < V <sub>DD</sub> - $25$ mV,<br>R <sub>L</sub> = $100$ kΩ, V <sub>DD</sub> = $5.5$ V |                                                                    | 85  |     |                        | 15    |

| Open-Loop Gain                  | Avol            | $150\text{mV} < V_{OUT} < V_{DD} - 150\text{mV},$ $R_L = 5k\Omega, V_{DD} = 5.5\text{V}$                     |                                                                    | 80  |     |                        | dB    |

| Contract Valle are Conin and II | V <sub>OH</sub> | V <sub>DD</sub> - V <sub>OUT</sub>                                                                           | $R_L = 100k\Omega$                                                 |     |     | 5                      | mV    |

| Output-Voltage-Swing High       |                 |                                                                                                              | $R_L = 5k\Omega$                                                   |     |     | 90                     |       |

| Output-Voltage-Swing Low        | V <sub>OL</sub> | $V_{OUT} - V_{SS}$ $ R_L = 100k\Omega $ $R_L = 5k\Omega $                                                    | $R_L = 100k\Omega$                                                 |     |     | 5                      | mV    |

| Output-voltage-Swilig Low       |                 |                                                                                                              |                                                                    |     | 90  | IIIV                   |       |

| SHDN_ Logic Low                 | Vu              | $V_{DD} = 1.8V \text{ to } 3.6V$                                                                             |                                                                    |     |     | 0.4                    | V     |

| 31 IDIV_ LOGIC LOW              | VIL             | V <sub>DD</sub> = 3.6V to 5.5V                                                                               |                                                                    |     |     | 0.8                    | v     |

| SHDN_ Logic High                | V               | $V_{DD} = 1.8V \text{ to } 3.6V$                                                                             |                                                                    | 1.4 |     |                        | V     |

|                                 | VIH             | V <sub>DD</sub> = 3.6V to 5.5V                                                                               |                                                                    | 2   |     |                        | V     |

| SHDN_ Input-Bias Current        | I <sub>IL</sub> | SHDN_ = V <sub>SS</sub>                                                                                      |                                                                    |     |     | 5                      | nA    |

| John Input-bids Current         | Iн              | SHDN_ = V <sub>DD</sub>                                                                                      |                                                                    |     |     | 1000                   | nA    |

| Output Leakage in Shutdown      | IOUT(SHDN_)     | $\overline{\text{SHDN}}_{-} = V_{SS},  \overline{V_{OUT}}$                                                   | SHDN_ = V <sub>SS</sub> , V <sub>OUT</sub> = 0V to V <sub>DD</sub> |     |     | 1000                   | nA    |

**Note 1:** Specifications are 100% tested at  $T_A = +25^{\circ}C$  (exceptions noted). All temperature limits are guaranteed by design.

Note 2: Guaranteed by design, not production tested.

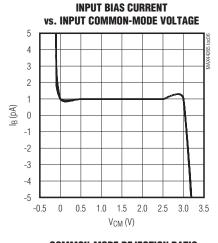

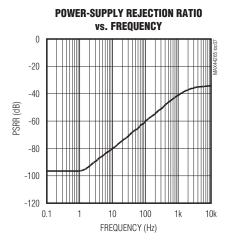

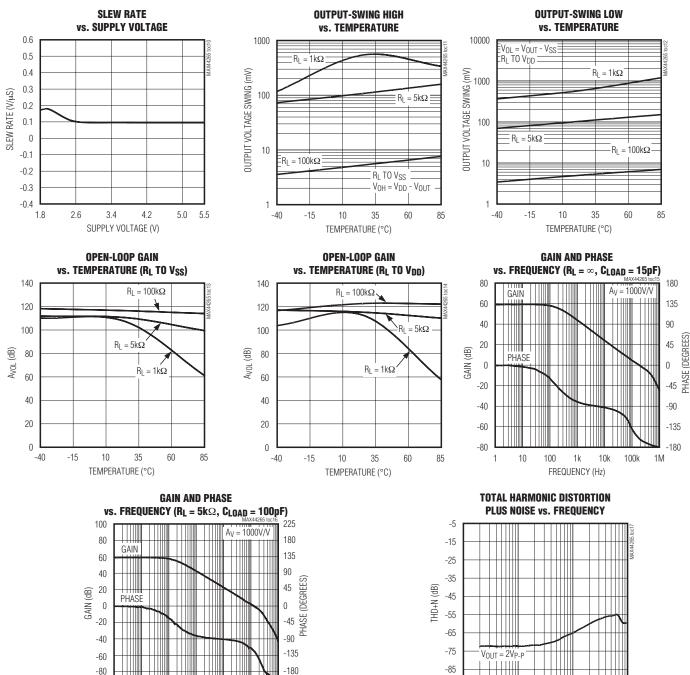

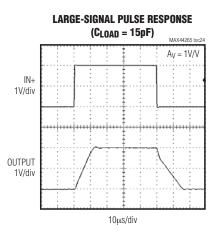

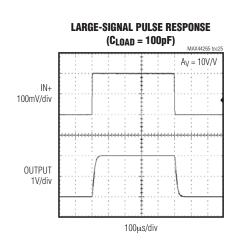

## **Typical Operating Characteristics**

(V<sub>DD</sub> = 3V, V<sub>SS</sub> = V<sub>CM</sub> = 0V, R<sub>L</sub> to V<sub>DD</sub>/2, T<sub>A</sub> = +25°C, unless otherwise noted.)

## \_Typical Operating Characteristics (continued)

$(V_{DD} = 3V, V_{SS} = V_{CM} = 0V, R_L \text{ to } V_{DD}/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

-225

-95

FREQUENCY (Hz)

-100

10

100

1k

FREQUENCY (Hz)

10k

100k

## Typical Operating Characteristics (continued)

$(V_{DD} = 3V, V_{SS} = V_{CM} = 0V, R_L \text{ to } V_{DD}/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

\_Typical Operating Characteristics (continued)

$(V_{DD} = 3V, V_{SS} = V_{CM} = 0V, R_L \text{ to } V_{DD}/2, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

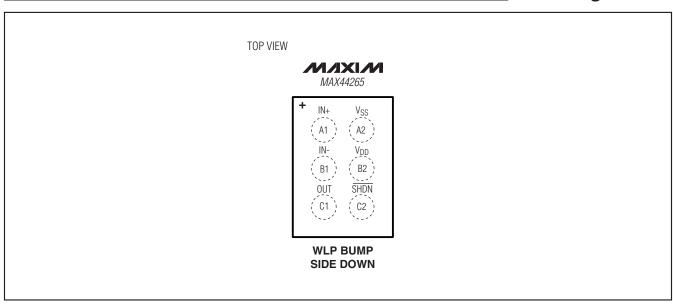

Pin Configuration

## **Pin Description**

| PIN | NAME            | FUNCTION                     |

|-----|-----------------|------------------------------|

| A1  | IN+             | Noninverting Amplifier Input |

| A2  | V <sub>SS</sub> | Negative Supply Voltage      |

| B1  | IN-             | Inverting Amplifier Input    |

| C1  | OUT             | Amplifier Output             |

| B2  | $V_{DD}$        | Positive Supply Voltage      |

| C2  | SHDN            | Shutdown                     |

### **Detailed Description**

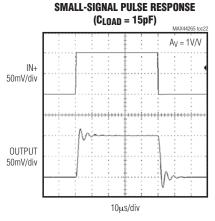

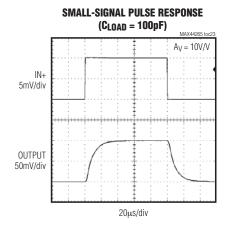

Featuring a maximized ratio of GBW to supply current, low operating supply voltage, low input bias current, and rail-to-rail inputs and outputs, the MAX44265 is an excellent choice for precision or general-purpose, low-current, low-voltage, battery-powered applications. This CMOS device consumes an ultra-low 4µA (typ) supply current and has a 200µV (typ) offset voltage. For additional power conservation, the IC features a low-power shutdown mode that reduces supply current to 1nA (typ) and puts the amplifier's output in a high-impedance state. This device is unity-gain stable with a 200kHz GBW product, driving capacitive loads up to 30pF. The capacitive load can be increased to 250pF when the amplifier is configured for a 10V/V gain.

### Rail-to-Rail Inputs and Outputs

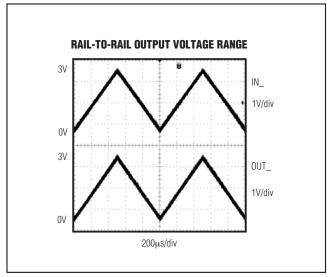

The IC has a parallel-connected n- and p-channel differential input stage that allows an input common-mode voltage range that extends 100mV beyond the positive and negative supply rails, with excellent common-mode rejection. The IC is capable of driving the output to within 5mV of both supply rails with a 100k $\Omega$  load. This device can drive a 5k $\Omega$  load with swings to within 60mV of the rails. Figure 1 shows the output voltage swing of the IC configured as a unity-gain buffer powered from a single 3V supply.

#### **Low Input Bias Current**

The IC features ultra-low 1pA (typ) input bias current. The variation in the input bias current is minimal with changes in the input voltage due to very high input impedance (in the order of  $1G\Omega$ ).

## Applications Information

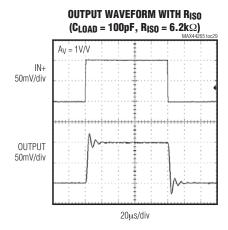

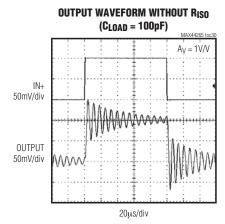

### **Driving Capacitive Loads**

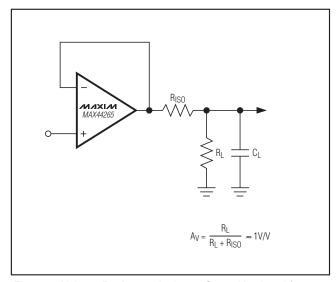

The IC's amplifier is unity-gain stable for loads up to 30pF. However, the capacitive load can be increased to 250pF when the amplifier is configured for a minimum gain of 10V/V. Applications that require greater capacitive-drive capability should use an isolation resistor between the output and the capacitive load (Figure 2). Also, in unity-gain applications with relatively small R<sub>L</sub> (approximately  $5k\Omega$ ), the capacitive load can be increased up to 200pF.

Figure 1. Rail-to-Rail Output Voltage Range

Figure 2. Using a Resistor to Isolate a Capacitive Load from the Op Amp

#### **Power-Supply Considerations**

The IC is optimized for single 1.8V to 5.5V supply operation. A high amplifier power-supply rejection ratio of 95dB (typ) allows the devices to be powered directly from a battery, simplifying design and extending battery life.

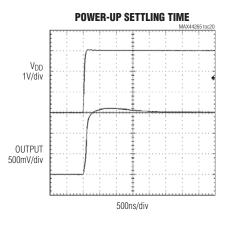

### **Power-Up Settling Time**

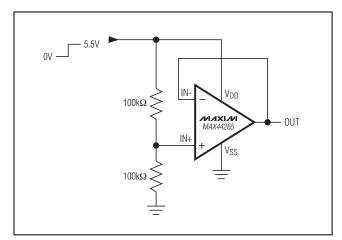

The IC typically requires  $5\mu s$  after power-up. Supply settling time depends on the supply voltage, the value of the bypass capacitor, the output impedance of the incoming supply, and any lead resistance or inductance between components. Op-amp settling time depends primarily on the output voltage and is slew-rate limited. Figure 3 shows MAX44265 in a noninverting voltage follower configuration with the input held at midsupply. The output settles in approximately 18 $\mu s$  for VDD = 3V (see the *Typical Operating Characteristics* for power-up settling time).

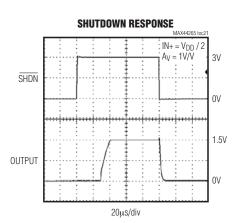

#### **Shutdown Mode**

The IC features an active-low shutdown input. The device enters shutdown in 2µs (typ) and exit in 30µs (typ). The amplifier's outputs are in a high-impedance state in shutdown mode. Drive SHDN low to enter shutdown. Drive SHDN high to enable the amplifier.

Figure 3. Power-Up Test Configuration

### **Power-Supply Bypassing and Layout**

To minimize noise, bypass  $V_{DD}$  with a  $0.1\mu F$  capacitor to ground, as close to the pin as possible.

Good layout techniques optimize performance by decreasing the amount of stray capacitance and inductance to the op amps' inputs and outputs. Minimize stray capacitance and inductance by placing external components close to the IC.

\_Chip Information

PROCESS: BiCMOS

### **Package Information**

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|--------------|--------------|----------------|---------------------|

| 6 WLP        | W61B1+1      | <u>21-0217</u> | _                   |

**Revision History**

| VISION<br>JMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|-----------------|---------------|-----------------|------------------|

| 0               | 12/10         | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.