### 产品特性

● 低功耗: 395 mW@125MSPS

● 电源电压: 1.8V

● 输出电平: 1.8 V CMOS 或 LVDS

● 信噪比(SNR)=76dBFS (Fin=70MHz/Fs=125MSPS)

无杂散动态范围(SFDR)=86dBc (Fin=70MHz/Fs=125MSPS)

● 内置 1 至 8 倍输入时钟整数分频器

● 小信号输入噪声: -153dBm/Hz (200Ω输入

阻抗 /Fin=70MHz/Fs=125MSPS)

可编程内部基准电压源

● 差分模拟输入范围: 1~2V 峰峰值

● 差分模拟输入带宽: 650MHz

● 内置时钟占空比调整器

● 串行端口(SPI)控制

● 用户可配置的内置测试(BIST)功能

● 节能的掉电模式

### 产品应用

- 雷达系统

- 分集无线电系统

- 多模式数字接受机 (3G)

- GSM / EDGE / W-CDMA / LTE / CDMA2000 /WiMAX / TD-SCDMA

- 智能天线系统

- 通用软件无线电

- 宽带数据应用

- 超声设备

### 概述

CBM92AD65 是 16 位、80/105/125 MSPS单通道模数转换器(ADC),旨在支持需要高性能、低成本、小尺寸且具有多功能性的通信应用。这款 ADC 内核采用多级、差分流水线架构,并集成了输出纠错逻辑,支持用户可选

的各种输入范围。集成基准电压源可简化设计。占空比稳定器可用来补偿 ADC 时钟占空比的波动,使转换器保持出色的性能。ADC 输出数据可以直接送至外部 16 位输出端口,这些输出可以设置为 1.8 V CMOS 或 LVDS。需要时,灵活的掉电选项可以明显降低功耗。设置与控制的编程利用三线式 SPI 兼容型串行接口来完成。芯片可采用 48 引脚 QFN 封装,额定温度范围为-40°C 至+85°C 工业温度范围。

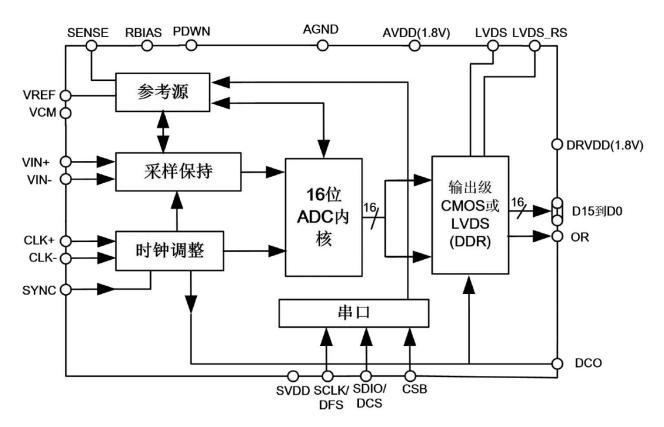

# 功能框图

图 1 CBM92AD65 功能框图

# 技术规格

# ADC 直流规格

除非另有说明,测试条件为AVDD = 1.8 V、DRVDD = 1.8 V、VIN = -1.0 dBFS 差分输入、1.0 V 内部基准电压、DCS 使能。

表1.

| <b>45.</b> Wh                    | 70.00 | СВ   | M92AD65 | -80   | CBN  | /192AD65- | -105  | CBN  | M92AD65 | -125  | 单位      |

|----------------------------------|-------|------|---------|-------|------|-----------|-------|------|---------|-------|---------|

| 参数                               | 温度    | 最小值  | 典型值     | 最大值   | 最小值  | 典型值       | 最大值   | 最小值  | 典型值     | 最大值   |         |

| 分辨率                              | 全     |      | 16      |       |      | 16        |       |      | 16      |       | 位       |

| <br>精度                           |       |      |         |       |      |           |       |      |         |       |         |

| 无失码                              | 全     |      | 保证      |       |      | 保证        |       |      | 保证      |       |         |

| 失调误差                             | 全     |      | ±0.06   | ±0.27 |      | ±0.06     | ±0.27 |      | ±0.06   | ±0.27 | % FSR   |

| 增益误差                             | 全     |      | ±0.23   | ±2.7  |      | ±0.23     | ±2.7  |      | ±0.5    | ±2.7  | % FSR   |

| 微分非线性(DNL) <sup>1</sup>          | 全     | -1.0 |         | ±1.35 | -1.0 |           | ±1.35 | -1.0 |         | ±1.35 | LSB     |

|                                  | 25℃   |      | ±0.7    |       |      | ±0.7      |       |      | ±0.8    |       | LSB     |

| 积分非线性(INL) <sup>1</sup>          | 全     |      |         | ±4    |      |           | ±5    |      |         | ±5    | LSB     |

|                                  | 25℃   |      | ±2.5    |       |      | ±3.0      |       |      | ±3.5    |       | LSB     |

| 温度漂移                             |       |      | •       | ,     |      | •         |       |      |         | '     |         |

| 失调误差                             | 全     |      | ±3      |       |      | ±3        |       |      | ±3      |       | ppm/°C  |

| 增益误差                             | 全     |      | ±16     |       |      | ±16       |       |      | ±16     |       | ppm/°C  |

| 内部基准电压                           |       |      |         |       |      | ,         |       |      |         |       |         |

| 输出电压误差(1V 模式)                    | 全     |      | ±9      | ±13   |      | ±9        | ±13   |      | ±9      | ±13   | mV      |

| 负载调整率@1.0mA                      | 全     |      | 3       |       |      | 3         |       |      | 3       |       | mV      |

| 输入端参考噪声                          |       |      |         |       |      |           |       |      |         |       |         |

| VREF = 1.0 V                     | 25℃   |      | 2.37    |       |      | 2.46      |       |      | 2.27    |       | LSB rms |

| 模拟输入                             |       |      |         |       |      |           |       |      |         |       |         |

| 输入范围,VREF = 1.0 V                | 全     |      | 2       |       |      | 2         |       |      | 2       |       | Vp-p    |

| 输入电容 <sup>2</sup>                | 全     |      | 7       |       |      | 7         |       |      | 7       |       | pF      |

| 输入共模电压                           | 全     |      | 0.9     |       |      | 0.9       |       |      | 0.9     |       | V       |

| 基准电压输入阻抗                         | 全     |      | 7       |       |      | 7         |       |      | 7       |       | kΩ      |

| 电源                               |       |      |         |       |      |           |       |      |         |       |         |

| 电源电压                             |       |      |         |       |      |           |       |      |         |       |         |

| AVDD                             | 全     | 1.7  | 1.8     | 1.9   | 1.7  | 1.8       | 1.9   | 1.7  | 1.8     | 1.9   | V       |

| DRVDD                            | 全     | 1.7  | 1.8     | 1.9   | 1.7  | 1.8       | 1.9   | 1.7  | 1.8     | 1.9   | V       |

| SVDD                             | 全     | 1.7  |         | 1.9   | 1.7  |           | 1.9   | 1.7  |         | 1.9   | V       |

| 电源电流                             |       |      |         |       |      |           |       |      |         |       |         |

| IAVDD <sup>1</sup>               | 全     |      | 129     | 135   |      | 171       | 179   |      | 197     | 205   | mA      |

| IDRVDD <sup>1</sup> (1.8 V CMOS) | 全     |      | 17      |       |      | 24        |       |      | 27      |       | mA      |

| IDRVDD <sup>1</sup> (1.8 V LVDS) | 全     |      | 45      |       |      | 48        |       |      | 51      |       | mA      |

| 功耗                               |       |      |         |       |      |           |       |      |         |       |         |

| 直流输入                             | 全     |      | 243     | 261   |      | 334       | 345   |      | 380     | 395   | mW      |

| 正弦波输入 <sup>1</sup> (CMOS)        | 全     |      | 257     |       |      | 350       |       |      | 400     |       | mW      |

| 正弦波输入 1( CMOS)                   | 全     |      | 310     |       |      | 400       |       |      | 450     |       | mW      |

| 待机功耗 <sup>3</sup>                | 全     |      | 57      |       |      | 57        |       |      | 57      |       | mW      |

| 掉电功耗                             | 全     |      | 0.07    | 0.18  |      | 0.07      | 0.18  |      | 0.07    | 0.18  | mW      |

### ADC 交流规格

除非另有说明,测试条件为 AVDD = 1.8 V、DRVDD = 1.8 V、VIN = -1.0 dBFS 差分输入、1.0V 内部基准电压、DCS 使能。

#### 表2.

| 5. W.                      |     | СВІ | M92AD65 | -80 | CBN | /192AD65- | 105 | CBI | M92AD65- | 125 | 单位   |

|----------------------------|-----|-----|---------|-----|-----|-----------|-----|-----|----------|-----|------|

| <b>参数</b>                  | 温度  | 最小值 | 典型值     | 最大值 | 最小值 | 典型值       | 最大值 | 最小值 | 典型值      | 最大值 |      |

| 信噪比(SNR)                   |     |     |         |     |     |           |     |     |          |     |      |

| $f_{IN} = 30 \text{ MHz}$  | 25℃ |     | 80      |     |     | 79.5      |     |     | 78.9     |     | dBFs |

| $f_{IN} = 70 \text{ MHz}$  | 25℃ |     | 79      |     |     | 79        |     |     | 78.9     |     | dBFs |

| $f_{IN} = 140 \text{ MHz}$ | 25℃ |     | 78.5    |     |     | 78        |     |     | 77       |     | dBFs |

| $f_{IN} = 200 \text{ MHz}$ | 25℃ |     | 77      |     |     | 76.5      |     |     | 75       |     | dBFs |

| 信纳比(SINAD)                 |     |     |         |     |     |           |     |     |          |     |      |

| $f_{IN} = 30 \text{ MHz}$  | 25℃ |     | 79.3    |     |     | 79.2      |     |     | 78.5     |     | dBFs |

| $f_{IN} = 70 \text{ MHz}$  | 25℃ |     | 79.3    |     |     | 78.4      |     |     | 78.5     |     | dBFs |

| $f_{IN} = 140 \text{ MHz}$ | 25℃ |     | 77      |     |     | 77.2      |     |     | 76.8     |     | dBFs |

| $f_{IN} = 200 \text{ MHz}$ | 25℃ |     | 76.2    |     |     | 75.5      |     |     | 74.3     |     | dBFs |

| 有效位数(ENOB)                 |     |     |         |     |     |           |     |     |          |     |      |

| $f_{IN} = 30 \text{ MHz}$  | 25℃ |     | 12.9    |     |     | 12.9      |     |     | 12.8     |     | 位    |

| $f_{IN} = 70 \text{ MHz}$  | 25℃ |     | 12.9    |     |     | 12.8      |     |     | 12.8     |     | 位    |

| $f_{IN} = 140 \text{ MHz}$ | 25℃ |     | 12.5    |     |     | 12.6      |     |     | 12.5     |     | 位    |

| $f_{IN} = 200 \text{ MHz}$ | 25℃ |     | 12.4    |     |     | 12.3      |     |     | 12.1     |     | 位    |

| 最差二次/三次谐波                  |     |     |         |     |     |           |     |     |          |     |      |

| $f_{IN} = 30 \text{ MHz}$  | 25℃ |     | -90.3   |     |     | -90.1     |     |     | -92.4    |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$  | 25℃ |     | -93.2   |     |     | -88.8     |     |     | -92.5    |     | dBc  |

| $f_{IN} = 140 \text{ MHz}$ | 25℃ |     | -81.8   |     |     | -85.8     |     |     | -88.6    |     | dBc  |

| $f_{IN} = 200 \text{ MHz}$ | 25℃ |     | -80.7   |     |     | -80.4     |     |     | -80.1    |     | dBc  |

| 无杂散动态范围(SFDR)              |     |     |         |     |     |           |     |     |          |     |      |

| $f_{IN} = 30 \text{ MHz}$  | 25℃ |     | 90.3    |     |     | 90.1      |     |     | 92.4     |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$  | 25℃ |     | 93.2    |     |     | 88.8      |     |     | 92.5     |     | dBc  |

| $f_{IN} = 140 \text{ MHz}$ | 25℃ |     | 81.8    |     |     | 85.8      |     |     | 88.7     |     | dBc  |

| $f_{IN} = 200 \text{ MHz}$ | 25℃ |     | 80.7    |     |     | 80.4      |     |     | 80.1     |     | dBc  |

<sup>&</sup>lt;sup>1</sup> 测量条件为: 低输入频率、满量程正弦波、每个输出位的负载约为 5pF。

$<sup>^2</sup>$  输入电容指一个差分输入引脚与AGND 之间的有效电容。

³ 待机功耗的测量条件为:直流输入、CLK 引脚无动作(设为 AVDD 或AGND)。

# 数字规格

除非另有说明,测试条件为 AVDD = 1.8 V、DRVDD = 1.8 V、VIN = -1.0dBFS 差分输入、1.0 V 内部基准电压、DCS 使能。

#### 表3.

| 参数                             | 温度 | 最小值  | 典型值              | 最大值  | 单位    |

|--------------------------------|----|------|------------------|------|-------|

| 差分时钟输入(CLK+、CLK-)              |    |      |                  |      |       |

| 逻辑兼容                           | 全  |      | CMOS/LVDS/LVPECL |      |       |

| 内部共模偏置                         | 全  |      | 0.9              |      | V     |

| 差分输入电压                         | 全  | 0.3  |                  | 3.6  | V p-p |

| 输入电压范围                         | 全  | AGND |                  | AVDD | V     |

| 输入共模范围                         | 全  | 0.9  |                  | 1.4  | V     |

| 高电平输入电流                        | 全  | -103 |                  | +103 | μΑ    |

| 低电平输入电流                        | 全  | -103 |                  | +103 | μΑ    |

| 输入电容                           | 全  |      | 4.5              |      | pF    |

| 输入电阻                           | 全  | 8.4  | 10.1             | 12.3 | kΩ    |

| 同步輸入                           |    |      |                  |      |       |

| 逻辑兼容                           | 全  |      | CMOS             |      |       |

| 内部偏置                           | 全  |      | 0.9              |      | V     |

| 输入电压范围                         | 全  | AGND |                  | AVDD | V     |

| 高电平输入电压                        | 全  | 1.2  |                  | AVDD | V     |

| 低电平输入电压                        | 全  | AGND |                  | 0.6  | V     |

| 高电平输入电流                        | 全  | -102 |                  | +103 | μΑ    |

| 低电平输入电流                        | 全  | -103 |                  | +104 | μΑ    |

| 输入电容                           | 全  |      | 1.2              |      | pF    |

| 输入电阻                           | 全  | 12.7 | 16.5             | 20.4 | kΩ    |

| 逻辑输入 (CSB) <sup>1</sup>        |    |      |                  |      |       |

| 高电平输入电压                        | 全  | 1.22 |                  | SVDD | V     |

| 低电平输入电压                        | 全  | 0    |                  | 0.6  | V     |

| 高电平输入电流                        | 全  | -12  |                  | 12   | μA    |

| 低电平输入电流                        | 全  | 43   |                  | 136  | μΑ    |

| 输入电阻                           | 全  |      | 26.8             |      | kΩ    |

| 输入电容                           | 全  |      | 2.3              |      | pF    |

| 逻辑输入 (SCLK/DFS) <sup>2</sup>   |    |      |                  |      |       |

| 高电平输入电压                        | 全  | 1.22 |                  | SVDD | V     |

| 低电平输入电压                        | 全  | 0    |                  | 0.6  | V     |

| 高电平输入电流(VIN=1.8V)              | 全  | -90  |                  | -142 | μΑ    |

| 低电平输入电流                        | 全  | -12  |                  | 12   | μΑ    |

| 输入电阻                           | 全  |      | 26.9             |      | kΩ    |

| 输入电容                           | 全  |      | 2.3              |      | pF    |

| 逻辑输入/输出(SDIO/DCS) <sup>1</sup> |    |      |                  |      |       |

| 高电平输入电压                        | 全  | 1.22 |                  | SVDD | V     |

| 低电平输入电压                             | 全 | 0    |      | 0.6  | V  |

|-------------------------------------|---|------|------|------|----|

| 高电平输入电流                             | 全 | -12  |      | -12  | μΑ |

| 低电平输入电流                             | 全 | 43   |      | 135  | μΑ |

| 输入电阻                                | 全 |      | 26.2 |      | kΩ |

| 输入电容                                | 全 |      | 3    |      | pF |

| 高电平输出电压                             | 全 | 1.70 |      |      | V  |

| 低电平输出电压                             | 全 |      |      | 0.2  | V  |

| 逻辑输入(OEB,PDWN,DITHER,LVDS,LVDS_RS)2 |   |      |      |      |    |

| 高电平输入电压                             | 全 | 1.22 |      | 2.1  | V  |

| 低电平输入电压                             | 全 | 0    |      | 0.6  | V  |

| 高电平输入电流(VIN=1.8V)                   | 全 | -95  |      | -139 | μΑ |

| 低电平输入电流                             | 全 | -12  |      | 12   | μΑ |

| 输入电阻                                | 全 |      | 26.4 |      | kΩ |

| 输入电容                                | 全 |      | 5.3  |      | pF |

| 数字输出(DRVDD=1.8V)                    |   |      |      |      |    |

| CMOS 模式                             |   |      |      |      |    |

| 高电平输出电压                             |   |      |      |      |    |

| IOH=50μA                            | 全 | 1.79 |      |      | V  |

| IOH=0.5mA                           | 全 | 1.75 |      |      | V  |

| 低电平输出电压                             |   |      |      |      |    |

| IOL=1.6mA                           | 全 |      |      | 0.2  | V  |

| IOL=50μA                            | 全 |      |      | 0.05 | V  |

| LVDS 模式                             |   |      |      |      |    |

| 差分输出电压(VOD),ANSI 模式                 | 全 | 290  | 345  | 400  | mV |

| 输出偏移电压(VOS), ANSI 模式                | 全 | 1.15 | 1.25 | 1.35 | V  |

| 差分输出电压(VOD),小摆幅模式                   | 全 | 160  | 200  | 230  | mV |

| 输出偏移电压(VOS),, 小摆幅模式                 | 全 | 1.15 | 1.25 | 1.35 | V  |

<sup>&</sup>lt;sup>1</sup>上拉。

<sup>2</sup>下拉。

### 开关规格

#### 表4.

| <b>65 W</b>                              | \= <del>-</del> | СВ   | M92AD65 | -80  | СВІ  | M92AD65- | -105 | CBN  | M92AD65- | 125 | 单位     |

|------------------------------------------|-----------------|------|---------|------|------|----------|------|------|----------|-----|--------|

| 参数                                       | 温度              | 最小值  | 典型值     | 最大值  | 最小值  | 典型值      | 最大值  | 最小值  | 典型值      | 最大值 |        |

| 时钟输入参数                                   |                 |      |         |      |      |          |      |      |          |     |        |

| 时钟输入速率                                   | 全               |      |         | 625  |      |          | 625  |      |          | 625 | MHz    |

| 转换速率 <sup>1</sup>                        |                 |      |         |      |      |          |      |      |          |     |        |

| DCS 使能                                   | 全               | 10   |         | 80   | 20   |          | 105  | 20   |          | 125 | MSPS   |

| DCS 禁用                                   | 全               | 10   |         | 80   | 10   |          | 105  | 10   |          | 125 | MSPS   |

| 时钟周期-分频模式(tclk)                          |                 | 12.5 |         |      | 9.5  |          |      | 8    |          |     | ns     |

| 时钟脉宽高电平(t <sub>CH</sub> )                |                 |      |         |      |      |          |      |      |          |     |        |

| 一分频模式, DCS 使能                            | 全               | 3.85 | 6.4     | 8.85 | 2.95 | 4.85     | 6.85 | 2.5  | 4.5      | 5.9 | ns     |

| 一分频模式, DCS 禁用                            | 全               | 6.05 | 6.35    | 6.75 | 4.55 | 4.85     | 5.1  | 3.9  | 4.5      | 4.9 | ns     |

| 二分频至八分频模式                                | 全               | 0.83 |         |      | 0.83 |          |      | 0.83 |          |     | ns     |

| 孔径延时(t <sub>A</sub> )                    | 全               |      | 1.3     |      |      | 1.3      |      |      | 1.3      |     | ns     |

| 孔径不确定(抖动,t <sub>J</sub> )                | 全               |      | 0.08    |      |      | 0.08     |      |      | 0.08     |     | ps rms |

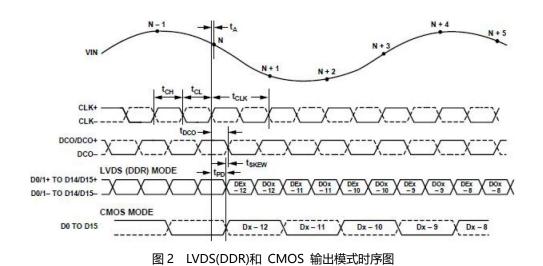

| 数据输出参数                                   |                 |      |         |      |      |          |      |      |          |     |        |

| CMOS 模式                                  |                 |      |         |      |      |          |      |      |          |     |        |

| 数据传播延时(t <sub>PD</sub> )                 | 全               | 2.3  | 2.9     | 3.5  | 2.3  | 2.9      | 3.5  | 2.3  | 2.9      | 3.5 | ns     |

| DCO 传播延时(t <sub>DCO</sub> )              | 全               | 2.6  | 3.5     | 4.4  | 2.6  | 3.5      | 4.4  | 2.6  | 3.5      | 4.4 | ns     |

| DCO 至数据偏斜(t <sub>SKEW</sub> )            | 全               | 0.3  | 0.7     | 0.9  | 0.3  | 0.7      | 0.9  | 0.3  | 0.7      | 0.9 | ns     |

| LVDS 模式                                  |                 |      |         |      |      |          |      |      |          |     |        |

| 数据传播延时(t <sub>PD</sub> )                 | 全               | 2.5  | 3.5     | 4.3  | 2.5  | 3.5      | 4.3  | 2.5  | 3.5      | 4.3 | ns     |

| DCO 传播延时(t <sub>DCO</sub> ) <sup>2</sup> | 全               | 3.3  | 3.7     | 4.4  | 3.3  | 3.7      | 4.4  | 3.3  | 3.7      | 4.4 | ns     |

| DCO 至数据偏斜(t <sub>SKEW</sub> )            | 全               | -0.3 | 0.5     | 1.3  | -0.3 | 0.5      | 1.5  | -0.3 | 0.5      | 1.3 | ns     |

| CMOS 模式流水线延时                             | 全               |      | 12      |      |      | 12       |      |      | 12       |     | 周期     |

| LVDS 模式流水线延时                             | 全               |      | 12.5    |      |      | 12.5     |      |      | 12.5     |     | 周期     |

| 唤醒时间 <sup>3</sup>                        | 全               |      | 503     |      |      | 503      |      |      | 503      |     | μs     |

| 超范围恢复时间                                  | 全               |      | 2       |      |      | 2        |      |      | 2        |     | 周期     |

<sup>1</sup> 转换速率指分频之后的时钟速率。

$<sup>^2</sup>$  写入 SPI 寄存器的位 0 至位 4 可以增加额外的 DCO 延迟时间。

<sup>3</sup> 唤醒时间指从掉电模式返回正常工作模式所需的时间。

### 时序规格

#### 表5.

| 参数                    | 条件                                     | 限值          |

|-----------------------|----------------------------------------|-------------|

| 同步时序要求                |                                        |             |

| t <sub>SSYNC</sub>    | SYNC 至CLK+建立时间的上升沿                     | 0.33 ns,典型值 |

| t <sub>HSYNC</sub>    | SYNC 至CLK+建立时间的上升沿                     | 0.42 ns,典型值 |

| SPI 时序要求              |                                        |             |

| t <sub>DS</sub>       | 数据与 SCLK 上升沿之间的建立时间                    | 2.2 ns,最小值  |

| t <sub>DH</sub>       | 数据与 SCLK 上升沿之间的保持时间                    | 2.2 ns,最小值  |

| t <sub>CLK</sub>      | SCLK 周期                                | 40.3 ns,最小值 |

| t <sub>S</sub>        | CSB 与 SCLK 之间的建立时间                     | 2.2 ns,最小值  |

| t <sub>H</sub>        | CSB 与 SCLK 之间的保持时间                     | 2.2 ns,最小值  |

| t <sub>HIGH</sub>     | SCLK 高电平脉冲宽度                           | 10.2 ns,最小值 |

| t <sub>LOW</sub>      | SCLK 低电平脉冲宽度                           | 10.2 ns,最小值 |

| t <sub>en_sdio</sub>  | 相对于 SCLK 下降沿, SDIO 引脚从输入状态切换到输出状态所需的时间 | 10.2 ns,最小值 |

| t <sub>DIS_SDIO</sub> | 相对于 SCLK 上升沿, SDIO 引脚从输出状态切换到输入状态所需的时间 | 10.2 ns,最小值 |

#### 时序图

8

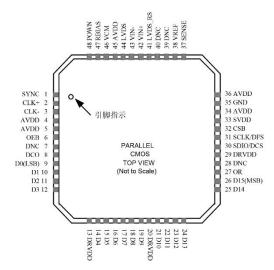

### 引脚配置与功能描述

标注: 封装底部的裸露热焊盘为器件提供模拟地。该焊盘必须与地相连,才能正常工作。

图 3. 并行 CMOS 引脚配置 (顶视图)

#### 表 6.引脚功能描述 (并行 CMOS 模式)

| 引脚编号         | 引脚名称                                    | 类型    | 描述                            |

|--------------|-----------------------------------------|-------|-------------------------------|

|              | איייייייייייייייייייייייייייייייייייייי | 大王    | 1時だ                           |

| ADC 电源       |                                         |       |                               |

| 13,20,29     | DRVDD                                   | 电源    | 数字输出驱动器电源(标称值 1.8 V)          |

| 4,5,34,36,45 | AVDD                                    | 电源    | 模拟电源 (标称值 1.8 V)              |

| 33           | SVDD                                    | 电源    | SPI 输入输出电源 (标称值 1.8 V)        |

| 7,28,39,40   | DNC                                     |       | 悬空管脚                          |

| 0            | AGND                                    | 地     | 封装底部的裸露热焊盘为器件提供模拟地。该焊盘必须与地相连。 |

| ADC 模拟       |                                         |       |                               |

| 42           | VIN+                                    | 输入    | 差分模拟输入引脚(+)                   |

| 43           | VIN-                                    | 输入    | 差分模拟输入引脚(-)                   |

| 38           | VREF                                    | 输入/输出 | 基准电压输入/输出                     |

| 37           | SENSE                                   | 输入    | 基准电压模式选择                      |

| 47           | RBIAS                                   | 输入/输出 | 外部基准偏置电阻                      |

| 46           | VCM                                     | 输出    | 模拟输入的共模电平偏置输出                 |

| 2            | CLK+                                    | 输入    | ADC 时钟输入(+)                   |

| 3            | CLK-                                    | 输入    | ADC 时钟输入(-)                   |

| 数字输入         | •                                       | •     |                               |

| 1            | SYNC                                    | 输入    | 数字同步引脚,仅用于从机模式                |

| 数字输出   |          |       |                                                 |

|--------|----------|-------|-------------------------------------------------|

| 9      | D0 (LSB) | 输出    | CMOS 输出数据                                       |

| 10     | D1       | 输出    | CMOS 输出数据                                       |

| 11     | D2       | 输出    | CMOS 輸出数据                                       |

| 12     | D3       | 输出    | CMOS 輸出数据                                       |

| 14     | D4       | 输出    | CMOS 輸出数据                                       |

| 15     | D5       | 输出    | CMOS 输出数据                                       |

| 16     | D6       | 输出    | CMOS 输出数据                                       |

| 17     | D7       | 输出    | CMOS 输出数据                                       |

| 18     | D8       | 输出    | CMOS 輸出数据                                       |

| 19     | D9       | 输出    | CMOS 输出数据                                       |

| 21     | D10      | 输出    | CMOS 輸出数据                                       |

| 22     | D11      | 输出    | CMOS 输出数据                                       |

| 23     | D12      | 输出    | CMOS 输出数据                                       |

| 24     | D13      | 输出    | CMOS 輸出数据                                       |

| 25     | D14      | 输出    | CMOS 輸出数据                                       |

| 26     | D15(MSB) | 输出    | CMOS 輸出数据                                       |

| 27     | OR       | 输出    | 超量程輸出                                           |

| 8      | DCO      | 输出    | 数据时钟输出                                          |

| SPI 控制 |          |       |                                                 |

| 31     | SCLK/DFS | 输入    | 在外部引脚模式下,SPI 串行时钟/数据格式选择引脚                      |

| 30     | SDIO/DCS | 输入/输出 | 在外部引脚模式下,SPI 串行数据输入/输出/占空比稳定器引脚                 |

| 32     | CSB      | 输入    | SPI 片选(低电平有效)                                   |

| ADC 配置 |          |       |                                                 |

| 6      | ОЕВ      | 输入    | 输出使能输入(低电平有效)引脚                                 |

| 48     | PDWN     | 输入    | 在外部引脚模式下,掉电输入引脚。在 SPI 模式下,此输入引脚可以配置为掉电或待机       |

|        |          |       | 引脚                                              |

| 35     | GND      | 地     | 该引脚接地。                                          |

| 41     | LVDS_RS  | 输入    | 在外部引脚模式下,降低 LVDS 输出幅度控制信号 (高电平有效), 在 SPI 模式下可以通 |

|        |          |       | 过 SPI 口控制。                                      |

| 44     | LVDS     | 输入    | 在外部引脚模式下,LVDS 模式使能控制信号(高电平有效),在SPI 模式下可以通过 SPI  |

|        |          |       | 口控制。                                            |

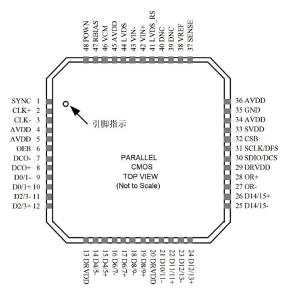

标注: 封装底部的裸露热焊盘为器件提供模拟地。该焊盘必须与地相连,才能正常工作。

图 4. 交错并行 LVDS 引脚配置 (顶视图)

#### 表 7. 引脚功能描述 (交错并行 LVDS 模式)

| 引脚编号         | 引脚名称  | 类型    | 描述                            |

|--------------|-------|-------|-------------------------------|

| ADC 电源       |       |       |                               |

| 13,20,29     | DRVDD | 电源    | 数字输出驱动器电源(标称值 1.8 V)          |

| 4,5,34,36,45 | AVDD  | 电源    | 模拟电源 (标称值 1.8 V)              |

| 33           | SVDD  | 电源    | SPI 输入输出电源 (标称值 1.8 V)        |

| 7,28,39,40   | DNC   |       | 悬空管脚                          |

| 0            | AGND  | 地     | 封装底部的裸露热焊盘为器件提供模拟地。该焊盘必须与地相连。 |

| ADC 模拟       |       |       |                               |

| 42           | VIN+A | 输入    | 差分模拟输入引脚(+)                   |

| 43           | VIN-A | 输入    | 差分模拟输入引脚(-)                   |

| 38           | VREF  | 输入/输出 | 基准电压输入/输出                     |

| 37           | SENSE | 输入    | 基准电压模式选择                      |

| 47           | RBIAS | 输入/输出 | 外部基准偏置电阻                      |

| 46           | VCM   | 输出    | 模拟输入的共模电平偏置输出                 |

| 2            | CLK+  | 输入    | ADC 时钟输入(+)                   |

| 3            | CLK-  | 输入    | ADC 时钟输入(-)                   |

| 数字输入         |       |       |                               |

| 1            | SYNC  | 输入    | 数字同步引脚,仅用于从机模式                |

| 数字输出         |       |       |                               |

| 10     | D0/1+    | 输出    | LVDS 输出数据 0/1(+)                                |

|--------|----------|-------|-------------------------------------------------|

| 9      | D0/1-    | 输出    | LVDS 输出数据 0/1(-)                                |

| 12     | D2/3+    | 输出    | LVDS 输出数据 2/3(+)                                |

| 11     | D2/3-    | 输出    | LVDS 输出数据 2/3(-)                                |

| 15     | D4/5+    | 输出    | LVDS 输出数据 4/5(+)                                |

| 14     | D4/5-    | 输出    | LVDS 输出数据 4/5(-)                                |

| 17     | D6/7+    | 输出    | LVDS 输出数据 6/7(+)                                |

| 16     | D6/7-    | 输出    | LVDS 输出数据 6/7(-)                                |

| 19     | D8/9+    | 输出    | LVDS 输出数据 8/9(+)                                |

| 18     | D8/9-    | 输出    | LVDS 输出数据 8/9(-)                                |

| 22     | D10/11+  | 输出    | LVDS 输出数据 10/11(+)                              |

| 21     | D10/11-  | 输出    | LVDS 输出数据 10/11(-)                              |

| 24     | D12/12+  | 输出    | LVDS 输出数据 12/13(+)                              |

| 23     | D12/13-  | 输出    | LVDS 输出数据 12/13(-)                              |

| 26     | D14/15+  | 输出    | LVDS 输出数据 14/15(+)                              |

| 25     | D14/15-  | 输出    | LVDS 输出数据 14/15(-)                              |

| 28     | OR+      | 输出    | 超量程输出+                                          |

| 27     | OR-      | 输出    | 超量程输出-                                          |

| 8      | DCO+     | 输出    | 数据时钟输出(+)                                       |

| 7      | DCO-     | 输出    | 数据时钟输出(-)                                       |

| SPI 控制 |          |       |                                                 |

| 31     | SCLK/DFS | 输入    | 在外部引脚模式下,SPI 串行时钟/数据格式选择引脚                      |

| 30     | SDIO/DCS | 输入/输出 | 在外部引脚模式下,SPI 串行数据输入/输出/占空比稳定器引脚                 |

| 32     | CSB      | 输入    | SPI 片选(低电平有效)                                   |

| ADC 配置 |          |       |                                                 |

| 6      | OEB      | 输入    | 输出使能输入(低电平有效)引脚                                 |

| 48     | PDWN     | 输入    | 在外部引脚模式下,掉电输入引脚。在 SPI 模式下,此输入引脚可以配置为掉电或待机       |

|        |          |       | 引脚                                              |

| 35     | GND      | 地     | 该引脚接地。                                          |

| 41     | LVDS_RS  | 输入    | 在外部引脚模式下,降低 LVDS 输出幅度控制信号 (高电平有效), 在 SPI 模式下可以通 |

|        |          |       | 过 SPI 口控制。                                      |

| 44     | LVDS     | 输入    | 在外部引脚模式下,LVDS 模式使能控制信号(高电平有效),在SPI 模式下可以通过 SPI  |

|        |          |       | 口控制。                                            |

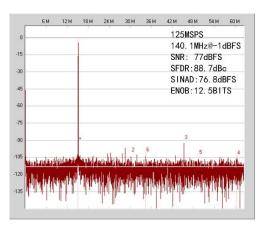

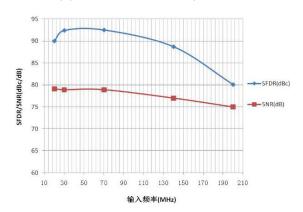

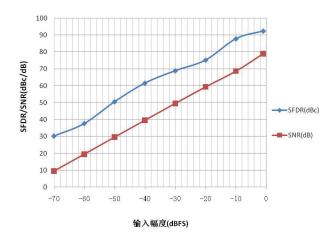

### 典型性能

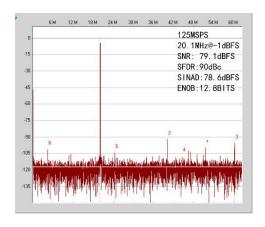

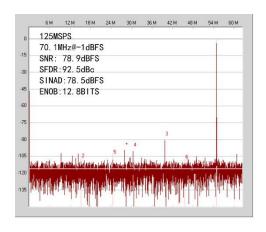

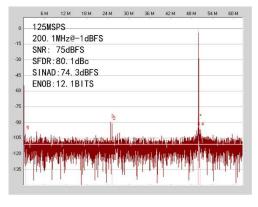

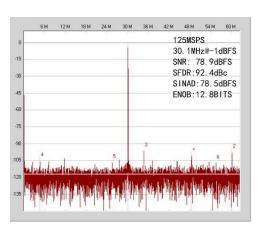

如无特别说明,测试条件如下: AVDD=1.8V,DRVDD=1.8V,SVDD=1.8V, 采样率 125MSPS, 2Vp-p 的差分输入, VIN=-1dBfs, TA=25℃。

图5 fin=20.1MHz 的单音 FFT

图7 fin=70.1MHz 的单音 FFT

图 9 fin=200.1MHz 的单音 FFT

图 6 fin=30.1MHz 的单音FFT

图 8 fin=140.1MHz 的单音 FFT

图10 SFDR、SNR 与输入频率的关系

图 11 SFDR、SNR 与输入幅度的关系(fin=30.1MHz)

### 工作原理

#### 输入共模

用户需要对器件进行设置,使得 VCM =  $0.5 \times \text{AVDD}$ (或 0.9 V)。芯片通过 VCM 引脚提供板上共模基准电压。通过 VCM 引脚提供模拟输入共模电压(典型值为 $0.5 \times \text{AVDD}$ )时,必须用一个  $0.1 \mu \text{F}$  电容对 VCM 引脚去耦到地。

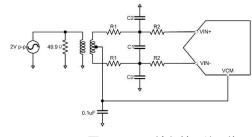

#### 差分输入配置

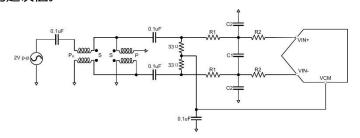

有两种输入配置: 1.使用的输入配置是差分变压器耦合,如图 12 的示例。为实现模拟输入偏置,须将VCM 电压连接到至变压器次级绕组的中心抽头处。2.使用的输入配置是差分双巴伦耦合,见图 13)。在这种配置中,输入交流耦合,CML 通过一个 33Ω电阻提供给各输入。这些电阻补偿输入巴伦的损耗,向驱动器提供 50Ω阻抗。表8 列出了设置RC 网络的建议值。

图 12 ADC 输入单巴伦网络

图 13 ADC 输入双巴伦网络

#### 表8. RC 网络示例

| 频率范围 (MHz) | 串联电阻R1 (Ω) | 差分电容C1 (pF) | 串联电阻 R2 (Ω) | 并联电容C2 (pF) |

|------------|------------|-------------|-------------|-------------|

| 0 到 100    | 15         | 18          | 15          | 断开10        |

| 100 到 300  | 10         | 10          | 10          |             |

### 基准电压源

CBM92AD65 内置稳定、精确的基准电压源。通过改变施加于 CBM92AD65 的基准电压(内部基准电压或外部基准电压),可以调整电压输入范围。ADC 输入范围跟随基准电压呈线性变化。在接下来的部分中,将对各种基准电压模式进行介绍。

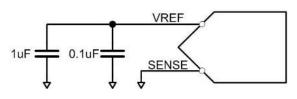

### 内部基准电压连接

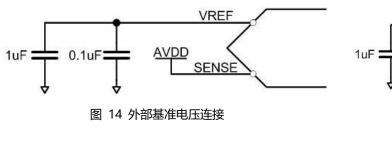

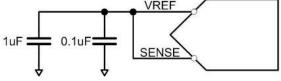

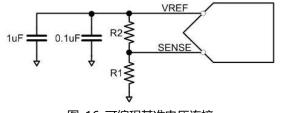

CBM92AD65 基准电压的总共有四种外围配置模式(见表 10)。第一种模式: SENSE 引脚接 AVDD, 见图 14,此时差分输入为 2.0Vp-p 满量程输入。第二种模式: 将SENSE 引脚与 VREF 引脚相连,见图15,可将基准放大器输出端切换至 SENSE 引脚,从而形成一个环路,提供0.5 V 基准输出电压(对于 1 V 峰峰值满量程输入)。第三种模式: 如果芯片与一个外部电阻分压器相连,则芯片内部开关也切换至 SENSE 引脚,则 VREF=0.5\*(1+R2/R1),如图 16。第四种模式: SENSE 引脚接地,则基准放大器开关与内部电阻分压器相连,见图 17,因而将 VREF 设为 1.0 V(对于 2.0 V 峰峰值满量程输入)。在这种模式下,SENSE接地,也可以通过 SPI 端口调整满量程,如表 9 所示。无论芯片使用内部基准电压还是外部基准电压,ADC 的电压输入范围始终是基准电压引脚(VREF)电压的两倍。如需利用 CBM92AD65 的内部基准电压来驱动多个转换器,从而提高增益的匹配度,则必须考虑到其它转换器对基准电压的负载。

图15 内部固定基准电压连接

图 16 可编程基准电压连接

图17 内部固定基准电压连接

# CBM92AD65 产品手册

# 16 位 80/105/125MSPS 单通道模数转换器

#### 表9. VREF 寄存器配置

| 寄存器地址 | 寄存器名        | Bit7     | Bit6   | Bit5~Bit0 | 默认值  |

|-------|-------------|----------|--------|-----------|------|

|       |             | 00=1.2   | 25Vp-p |           |      |

| 0x18  | 010 VDEF \\ | 01=1.    | 5V p-p | 禁用        | 0Xc0 |

| 0.00  | VREF 选择     | 10=1.7   | 75Vp-p | 赤用        |      |

|       |             | 11=2V p- | p (默认) |           |      |

#### 表10. 基准电压配置总汇

| 所选模式     | SENSE 电压    | 相应的 VREF (V)  | 相应的差分范围(Vp-p) |

|----------|-------------|---------------|---------------|

| 外部基准电压   | AVDD        | N/A           | 2*外部基准电压      |

| 内部固定基准电压 | VREF        | 0.5           | 1.0           |

| 可编程基准电压  | 0.2 到VREF   | 0.5*(1+R2/R1) | 2*VREF        |

| 内部固定基准电压 | AGND 到 0.2V | 1.0           | 2.0           |

### 时钟输入

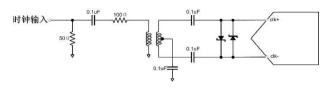

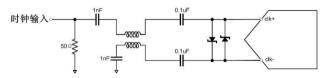

CMOS、LVDS、LVPECL 或正弦波信号均可作为 CBM92AD65 时钟输入信号。CLK+和 CLK-引脚有内部偏置,无需外部偏置。图 18 和图 19 显示两种为 CBM92AD65 提供时钟信号的首选方案(时钟速率可达 625 MHz)。利用射频巴伦或射频变压器,可将低抖动时钟源的单端信号转换成差分信号。对于625 MHz 的时钟频率,采用射频巴伦配置;对于 10 MHz 至 200 MHz 的时钟频率,采用射频变压器配置。跨接在变压器/巴伦次级上的背对背肖特基二极管可以将输入到 CBM92AD65 中的时钟信号限制为约差分 0.8V 峰峰值。

图 18 变压器时钟驱动连接

图 19 巴伦时钟驱动连接

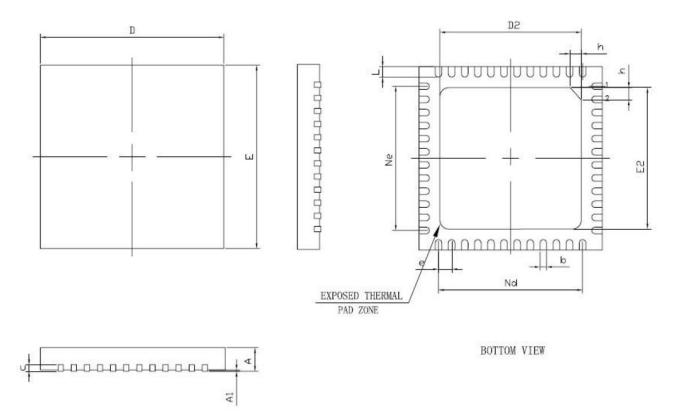

# 封装外形尺寸

标注: 以上尺寸单位为 mm

| SYMBOL | MILLIMETER |      |         | CVMPOL  | MILLIMETER |      |      |

|--------|------------|------|---------|---------|------------|------|------|

|        | MIN        | NOM  | MAX     | SYMBOL  | MIN        | NOM  | MAX  |

| Α      | 0.70       | 0.75 | 0.80    | Ne      | 5.50 BSC   |      |      |

| A1     |            | 0.02 | 0.05    | Nd      | 5.50 BSC   |      |      |

| b      | 0.18       | 0.25 | 0.30    | E       | 6.90       | 7.00 | 7.10 |

| С      | 0.18       | 0.20 | 0.23    | E2      | 5.30       | 5.40 | 5.50 |

| D      | 6.90       | 7.00 | 7.10    | L       | 0.35       | 0.40 | 0.45 |

| D2     | 5.30       | 5.40 | 5.50    | h       | 0.30       | 0.35 | 0.40 |

| е      | 0.50 BSC   |      | L/F载体尺寸 | 224×224 |            |      |      |

# PACKAGE/ORDERING INFORMATION

| PRODUCT | ORDERING<br>NUMBER | TEMPRANGE   | PACKAGE | PAKEAGE<br>MARKING | TRANSPOT<br>MEDIA,QUANTILY |

|---------|--------------------|-------------|---------|--------------------|----------------------------|

|         | CBM92AD65-80       | -40°C +85°C | QFN-48  | 92AD65-80          | Reel.260                   |

|         | CBM92AD65-105      | -40°C +85°C | QFN-48  | 92AD65-105         | Reel.260                   |

|         | CBM92AD65-125      | -40°C +85°C | QFN-48  | 92AD65-125         | Reel.260                   |