# 1MHZ CMOS Rail-to-Rail IO Opamp with RF Filter

### **Features**

Single-Supply Operation from +2.1V ~ +5.5V

• Rail-to-Rail Input / Output

Gain-Bandwidth Product: 1MHz (Typ.)

• Low Input Bias Current: 1pA (Typ.)

Low Offset Voltage: 3.5mV (Max.)

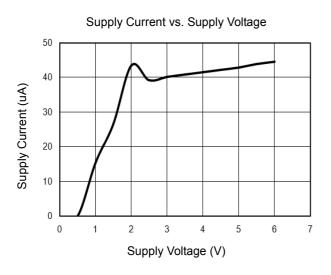

Quiescent Current: 40µA per Amplifier (Typ.)

Operating Temperature: -40°C ~ +125°C

• Embedded RF Anti-EMI Filter

# **General Description**

The LMV602 have a high gain-bandwidth product of 1MHz, a slew rate of  $0.6\text{V}/\,\mu\,\text{s}$ , and a quiescent current of  $40\,\mu\,\text{A}/\,\mu$  A/amplifier at 5V. The LMV602 is designed to provide optimal performance in low voltage and low noise systems. They provide rail-to-rail output swing into heavy loads. The input common mode voltage range includes ground, and the maximum input offset voltage is 3.5mV for LMV602. They are specified over the extended industrial temperature range (-40  $^{\circ}$ C to +125 $^{\circ}$ C). The operating range is from 2.1V to 5.5V. The LMV602 Dual is available in Green SOP-8, DIP-8 and DFN-8 packages.

### **Applications**

- ASIC Input or Output Amplifier

- Sensor Interface

- Medical Communication

- Smoke Detectors

- Audio Output

- Piezoelectric Transducer Amplifier

- Medical Instrumentation

- Portable Systems

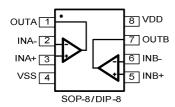

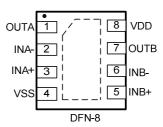

### **Pin Configuration**

Figure 1. LMV602 Pin Assignment Diagram

# **Absolute Maximum Ratings**

| Condition                                         | Min      | Max                   |  |  |  |

|---------------------------------------------------|----------|-----------------------|--|--|--|

| Power Supply Voltage (V <sub>DD</sub> to Vss)     | -0.5V    | +7.5V                 |  |  |  |

| Analog Input Voltage (IN+ or IN-)                 | Vss-0.5V | V <sub>DD</sub> +0.5V |  |  |  |

| PDB Input Voltage                                 | Vss-0.5V | +7V                   |  |  |  |

| Operating Temperature Range                       | -40°C    | +125°C                |  |  |  |

| Junction Temperature                              | +160°C   |                       |  |  |  |

| Storage Temperature Range                         | -55°C    | +150°C                |  |  |  |

| Lead Temperature (soldering, 10sec)               | +260°C   |                       |  |  |  |

| Package Thermal Resistance (T <sub>A</sub> =+25℃) | ·        |                       |  |  |  |

| SOP-8, θ <sub>JA</sub>                            | 125°C/W  |                       |  |  |  |

| MSOP-8, θ <sub>JA</sub>                           | 216°C/W  |                       |  |  |  |

| ESD Susceptibility                                |          |                       |  |  |  |

| НВМ                                               | 6KV      |                       |  |  |  |

| ММ                                                | 300V     |                       |  |  |  |

**Note:** Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Electrical Characteristics**

(At  $V_S$  = +5V,  $R_L$  = 100 $k\Omega$  connected to  $V_S/2$ , and  $V_{OUT}$  =  $V_S/2$ , unless otherwise noted.)

| PARAMETER                      | SYMBOL                   | CONDITIONS                                             | TYP          | MIN/MAX OVER TEMPERATURE |              |                |         |

|--------------------------------|--------------------------|--------------------------------------------------------|--------------|--------------------------|--------------|----------------|---------|

|                                |                          |                                                        | +25℃         | +25℃                     | -40℃ to +85℃ | UNITS          | MIN/MAX |

| INPUT CHARACTERISTICS          |                          |                                                        |              | I.                       |              |                | l.      |

| Input Offset Voltage           | Vos                      | $V_{CM} = V_S/2$                                       | 0.4          | 3.5                      | 5.6          | mV             | MAX     |

| Input Bias Current             | I <sub>B</sub>           |                                                        | 1            |                          |              | pA             | TYP     |

| Input Offset Current           | los                      |                                                        | 1            |                          |              | pA             | TYP     |

| Common-Mode Voltage Range      | V <sub>CM</sub>          | V <sub>S</sub> = 5.5V                                  | -0.1 to +5.6 |                          |              | V              | TYP     |

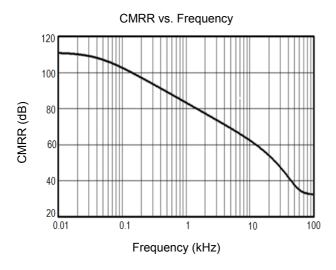

| Common-Mode Rejection Ratio    | CMRR                     | V <sub>S</sub> = 5.5V, V <sub>CM</sub> = -0.1V to 4V   | 70           | 62                       | 62           | dB             | MIN     |

|                                |                          | V <sub>S</sub> = 5.5V, V <sub>CM</sub> = -0.1V to 5.6V | 68           | 56                       | 55           |                |         |

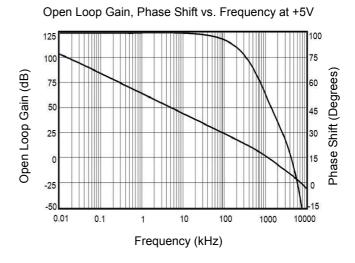

| Open-Loop Voltage Gain         | A <sub>OL</sub>          | $R_L = 5k\Omega$ , $V_O = +0.1V$ to +4.9V              | 80           | 70                       | 70           | dB             | MIN     |

|                                |                          | $R_L = 10k\Omega$ , $V_O = +0.1V$ to $+4.9V$           | 100          | 90                       | 85           |                |         |

| Input Offset Voltage Drift     | $\Delta V_{OS}/\Delta_T$ |                                                        | 2.7          |                          |              | μV/°C          | TYP     |

| OUTPUT CHARACTERISTICS         |                          |                                                        |              |                          |              |                |         |

| Output Voltage Swing from Rail | V <sub>OH</sub>          | $R_L = 100k\Omega$                                     | 4.997        | 4.990                    | 4.980        | V              | MIN     |

|                                | V <sub>OL</sub>          | R <sub>L</sub> = 100kΩ                                 | 3            | 10                       | 20           | mV             | MAX     |

|                                | V <sub>OH</sub>          | $R_L = 10k\Omega$                                      | 4.992        | 4.970                    | 4.960        | V              | MIN     |

|                                | V <sub>OL</sub>          | $R_L = 10k\Omega$                                      | 8            | 30                       | 40           | mV             | MAX     |

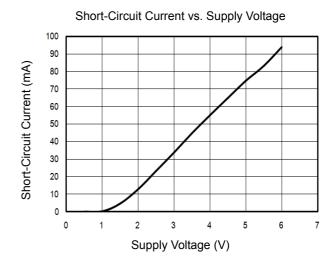

| Output Current                 | I <sub>SOURCE</sub>      | $R_L = 10\Omega$ to $V_S/2$                            | 84           | 60                       | 45           | mA             | MIN     |

|                                | I <sub>SINK</sub>        |                                                        | 75           | 60                       | 45           |                |         |

| POWER SUPPLY                   |                          |                                                        |              |                          |              |                |         |

| Operating Voltage Range        |                          |                                                        |              | 2.1                      | 2.5          | V              | MIN     |

|                                |                          |                                                        |              | 5.5                      | 5.5          | V              | MAX     |

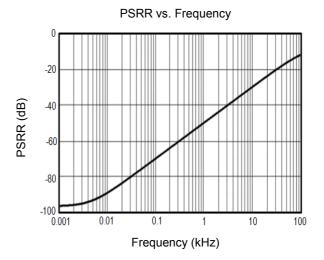

| Power Supply Rejection Ratio   | PSRR                     | $V_S$ = +2.5V to +5.5V, $V_{CM}$ = +0.5V               | 82           | 60                       | 58           | dB             | MIN     |

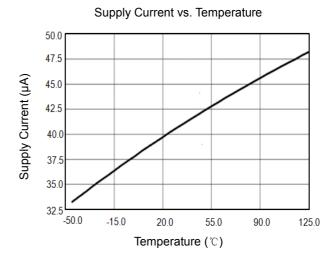

| Quiescent Current / Amplifier  | ΙQ                       |                                                        | 40           | 60                       | 80           | μA             | MAX     |

| DYNAMIC PERFORMANCE (CL        | . = 100pF)               |                                                        |              |                          |              |                |         |

| Gain-Bandwidth Product         | GBP                      |                                                        | 1            |                          |              | MHz            | TYP     |

| Slew Rate                      | SR                       | G = +1, 2V Output Step                                 | 0.6          |                          |              | V/µs           | TYP     |

| Settling Time to 0.1%          | ts                       | G = +1, 2V Output Step                                 | 5            |                          |              | μs             | TYP     |

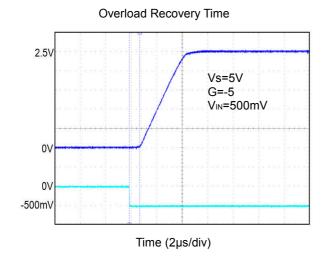

| Overload Recovery Time         |                          | V <sub>IN</sub> ·Gain = V <sub>S</sub>                 | 2.6          |                          |              | μs             | TYP     |

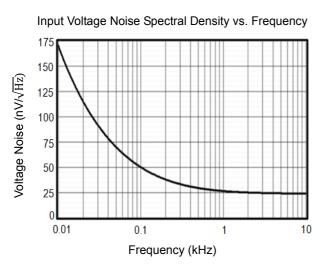

| NOISE PERFORMANCE              |                          |                                                        |              |                          |              |                |         |

| Voltage Noise Density          | e <sub>n</sub>           | f = 1kHz                                               | 27           |                          |              | $nV/\sqrt{Hz}$ | TYP     |

|                                |                          | f = 10kHz                                              | 20           |                          |              | $nV/\sqrt{Hz}$ | TYP     |

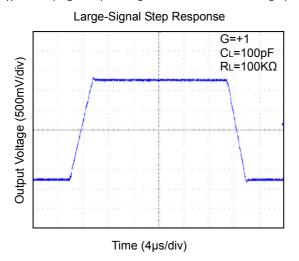

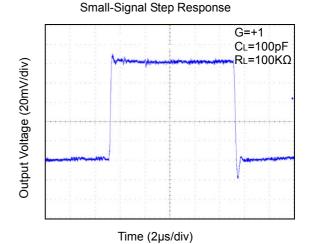

# **Typical Performance characteristics**

At  $T_A$ =+25°C,  $V_S$ =+5V, and  $R_L$ =100K $\Omega$  connected to  $V_S$ /2, unless otherwise noted.

# **Typical Performance characteristics**

At  $T_A$ =+25°C,  $V_S$ =+5V, and  $R_L$ =100K $\Omega$  connected to  $V_S/2$ , unless otherwise noted.

### **Application Note**

### **Power Supply Bypassing and Board Layout**

LMV602 series operates from a single 2.1V to 5.5V supply or dual  $\pm 1.05$ V to  $\pm 2.75$ V supplies. For best performance, a 0.1 $\mu$ F ceramic capacitor should be placed close to the  $V_{DD}$  pin in single supply operation. For dual supply operation, both  $V_{DD}$  and  $V_{SS}$  supplies should be bypassed to ground with separate 0.1 $\mu$ F ceramic capacitors.

#### **Low Supply Current**

The low supply current (typical 40uA per channel) of LMV602 will help to maximize battery life. They are ideal for battery powered systems

### **Operating Voltage**

LMV602 operates under wide input supply voltage (2.1V to 5.5V). In addition, all temperature specifications apply from -40 °C to +125 °C. Most behavior remains unchanged throughout the full operating voltage range. These guarantees ensure operation throughout the single Li-lon battery lifetime

### Rail-to-Rail Input

The input common-mode range of LMV602 extends 100mV beyond the supply rails ( $V_{SS}$ -0.1V to  $V_{DD}$ +0.1V). This is achieved by using complementary input stage. For normal operation, inputs should be limited to this range.

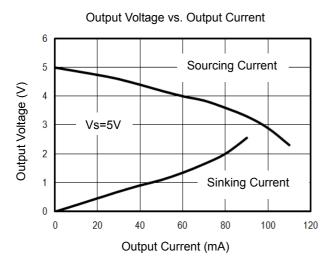

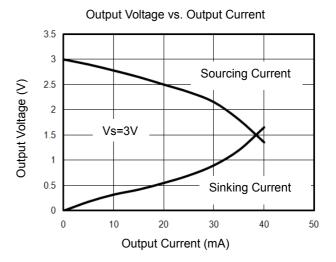

### **Rail-to-Rail Output**

Rail-to-Rail output swing provides maximum possible dynamic range at the output. This is particularly important when operating in low supply voltages. The output voltage of LMV602 can typically swing to less than 5 mV from supply rail in light resistive loads (> $100k\Omega$ ), and 30mV of supply rail in moderate resistive loads ( $10k\Omega$ ).

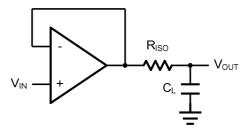

#### **Capacitive Load Tolerance**

The LMV602 is optimized for bandwidth and speed, not for driving capacitive loads. Output capacitance will create a pole in the amplifier's feedback path, leading to excessive peaking and potential oscillation. If dealing with load capacitance is a requirement of the application, the two strategies to consider are (1) using a small resistor in series with the amplifier's output and the load capacitance and (2) reducing the bandwidth of the amplifier's feedback loop by increasing the overall noise gain. Figure 2. shows a unity gain follower using the series resistor strategy. The resistor isolates the output from the capacitance and, more importantly, creates a zero in the feedback path that compensates for the pole created by the output capacitance.

Figure 2. Indirectly Driving a Capacitive Load Using Isolation Resistor

The bigger the  $R_{ISO}$  resistor value, the more stable  $V_{OUT}$  will be. However, if there is a resistive load  $R_L$  in parallel with the capacitive load, a voltage divider (proportional to  $R_{ISO}/R_L$ ) is formed, this will result in a gain error.

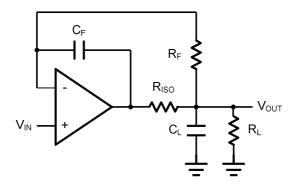

The circuit in *Figure 3* is an improvement to the one in *Figure 2*.  $R_F$  provides the DC accuracy by feed-forward the  $V_{IN}$  to  $R_L$ .  $C_F$  and  $R_{ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving the phase margin in the overall feedback loop. Capacitive drive can be increased by increasing the value of  $C_F$ . This in turn will slow down the pulse response.

Figure 3. Indirectly Driving a Capacitive Load with DC Accuracy